# iMX6 Rex Development Baseboard Manual

(version 0.2)

www.iMX6Rex.com

Contact: info@iMX6Rex.com

# Table of content

| Getting started                | 3 |

|--------------------------------|---|

| Connectors                     |   |

| Jumpers                        |   |

| LEDs & Buttons                 |   |

| Peripheral selection resistors |   |

## **Getting started**

These steps will help you to power up your iMX6 Rex development kit for the very first time.

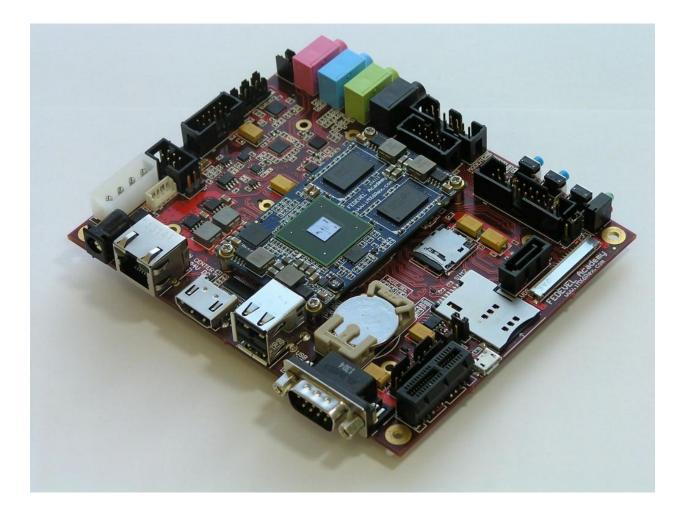

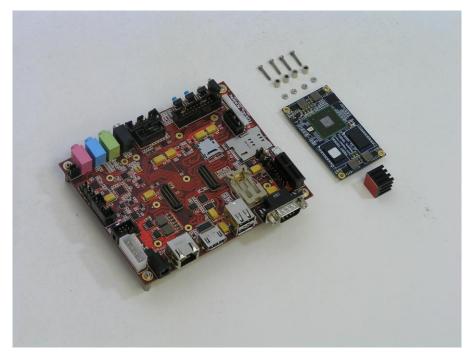

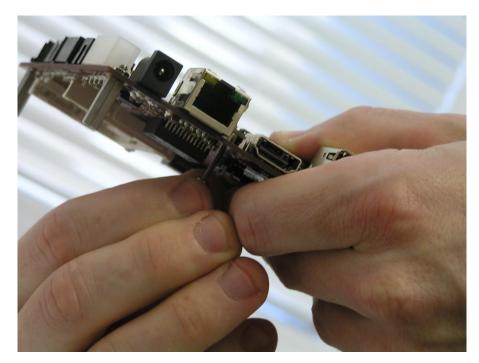

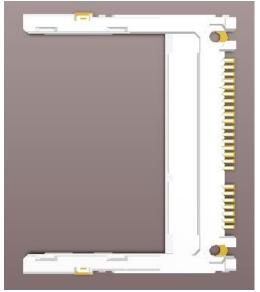

#### 1. Plug the module into the baseboard

These are the important parts to build the kit:

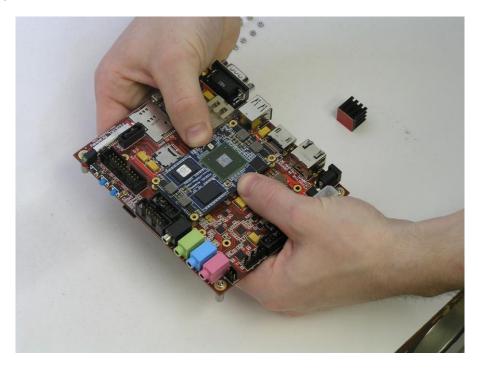

Notice the position of the thumbs:

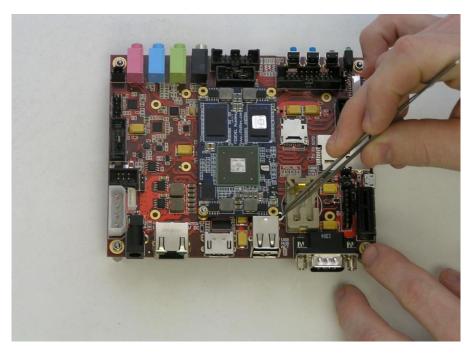

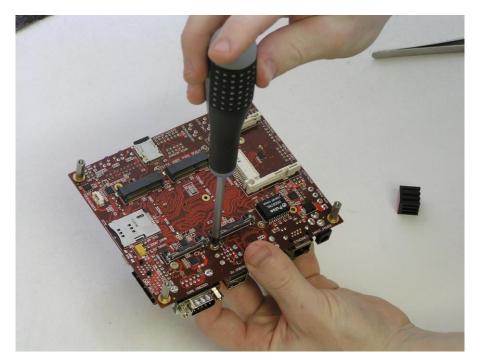

# 2. Add spacers and tight up all the four screws

Notice how the spacer is moved between the module and baseboard:

Plug a screw into the mounting hole and secure it with a nut:

Use a screwdriver to tight it up:

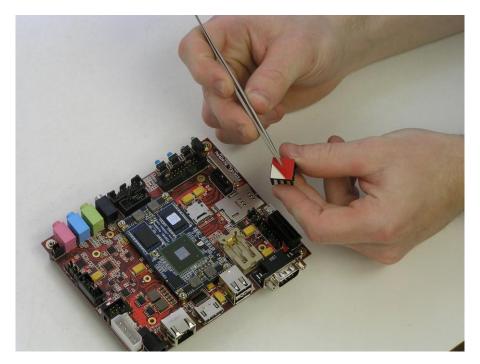

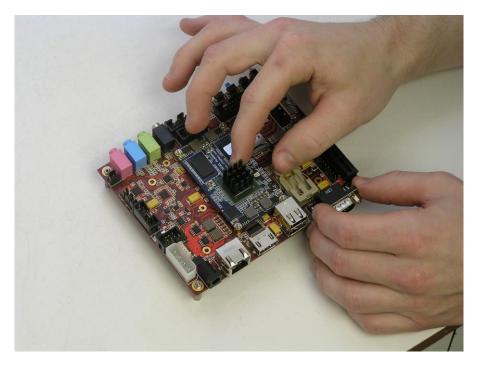

## 3. Place the heatsink

Remove the red protection foil from the heatsink:

Place the heatsink on the top of the processor:

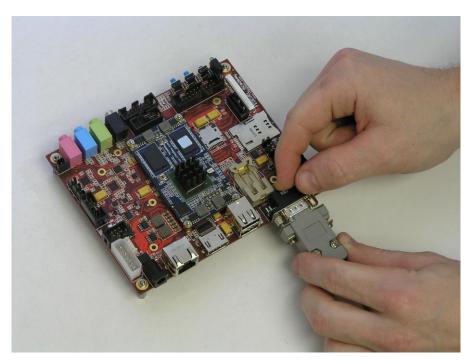

#### 4. Connect serial cable

Connect the iMX6 Rex RS232 serial port to your computer. Use the cable from development kit (it has to be a null modem cable with crossed wires). Run Hyperterminal (or download and use <u>Tera Term</u>).

Set the following serial port parameters – Baud rate: 115200 / Data: 8 / Parity: none / Stop bit: 1 / Flow control: none.

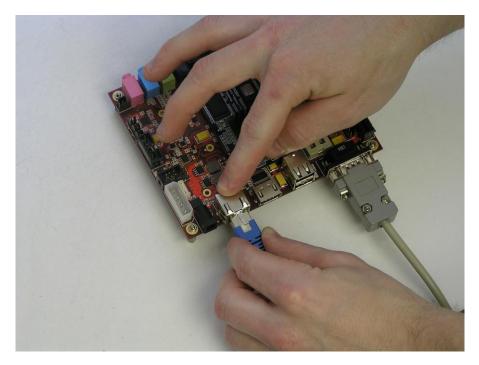

## 5. Connect network cable

Use the network cable delivered with your development kit (this cable is rated for 1Gb Ethernet). Connect the cable between your iMX6 Rex development kit and a network switch (possibly a computer).

Connecting the baseboard to a network is not required, but missing network may slow down booting process as Linux will be waiting for a DHCP answer.

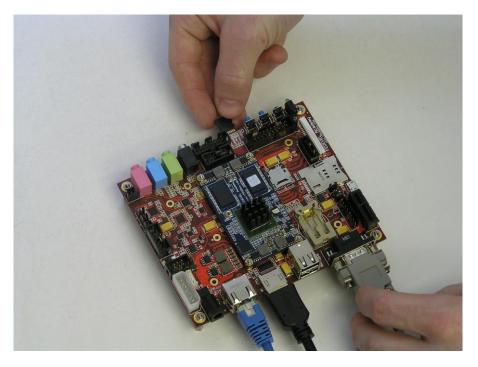

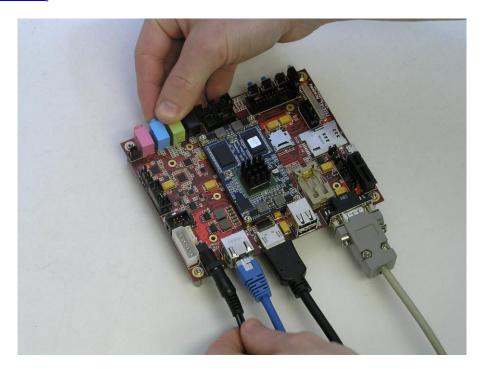

#### 6. Insert SD card

Insert the SD card delivered with your development kit into the slot placed on the edge of the board. Be sure the other SD card slot is empty.

# 7. Connect the power

You have two options, how the board may be powered. Be sure, your power supply can deliver enough power!

#### Option 1:

Use a 7V to 24V DC adapter (usually 12V/3A is fine – here is one from Farnell <u>VEP36US12</u>) with a power jack. The plug diameters are 2mm x 5.5mm with the positive voltage in the middle (*use e.g.* <u>Switchcraft S-760</u>).

#### Option 2:

Use an ATX power supply

#### 8. Update network configuration

After you connect the power, the board will start. Watch the console messages in your PC terminal. Once you see how the u-Boot autostart is counting down, press any key (e.g. ENTER) to interrupt it. Update the u-boot parameters based on your company network setting. Here is an example:

```

> setenv gateway '192.168.1.1'

> setenv netmask '255.255.255.0'

> setenv ipaddr '192.168.1.78'

```

Select a valid IP address from your network to use an initial ping and insert this command:

> setenv bootcmd 'ping 192.168.1.1; run bootcmd\_mmc'

In the case your server does not support DHCP, set a fixed IP address and network mask which will be assigned to the Rex board after it boots up into the Linux:

```

> setenv bootargs_mmc 'setenv bootargs ${bootargs}

ip=192.168.1.78:::255.255.255.0 root=/dev/mmcblk0p1 rootwait'

```

Save the u-boot parameters and restart the board:

> saveenv; reset

#### 9. Tada!

Now, your board should boot up into Linux. In case you have any problems to setup your Development kit, check out our <u>FORUM & Questions</u> or <u>contact us</u>. Enjoy!

www.iMX6Rex.com

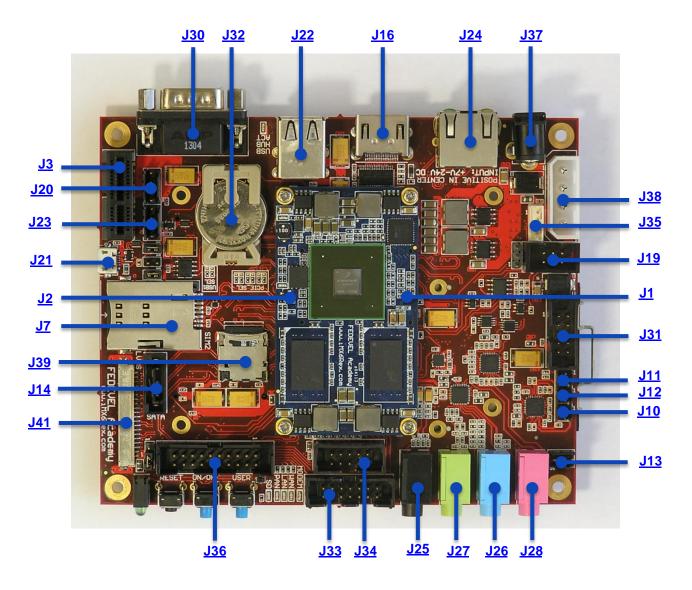

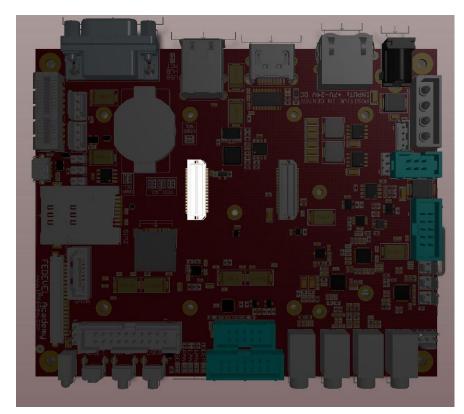

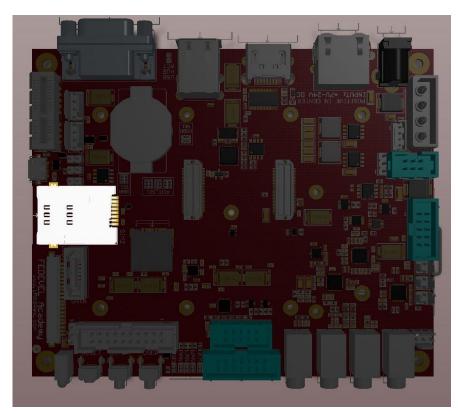

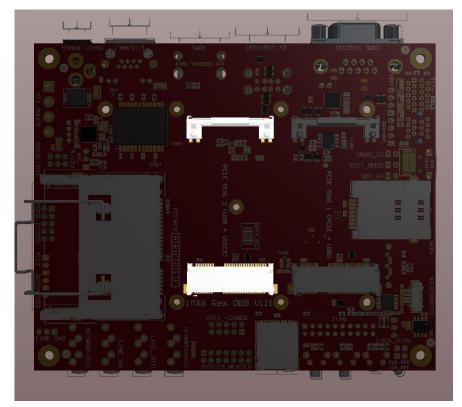

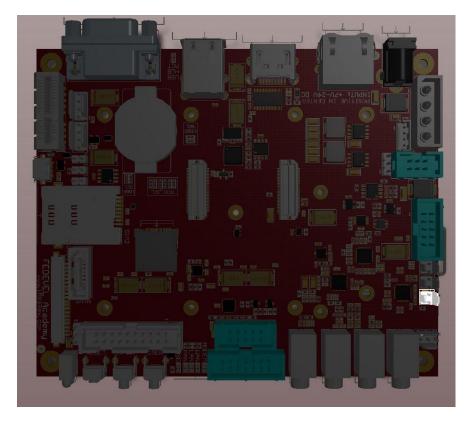

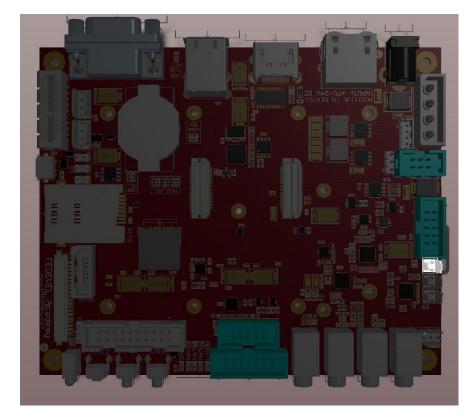

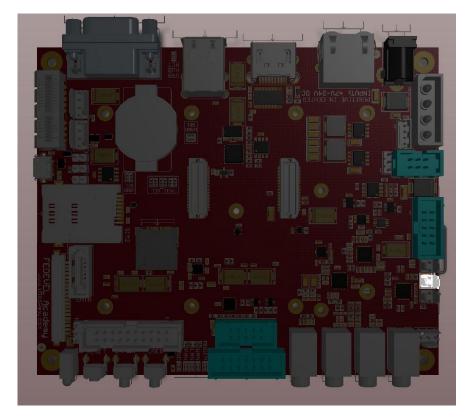

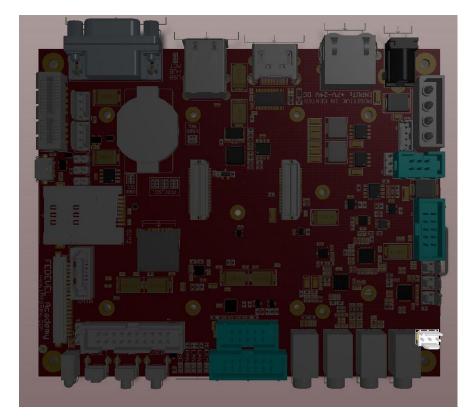

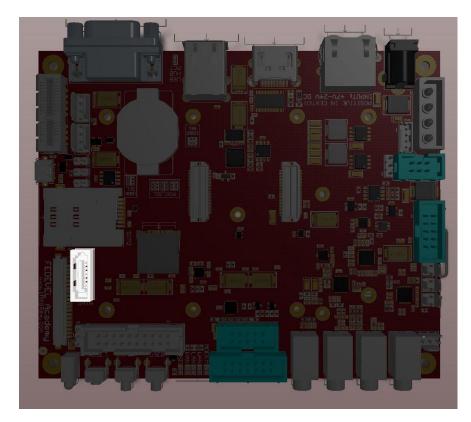

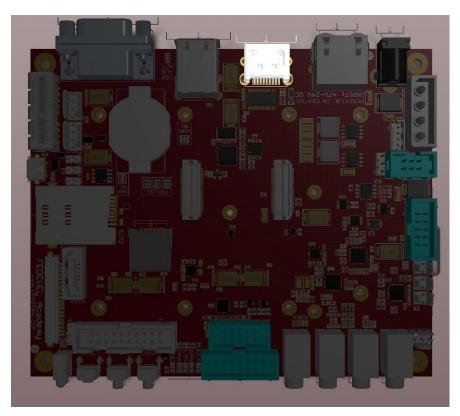

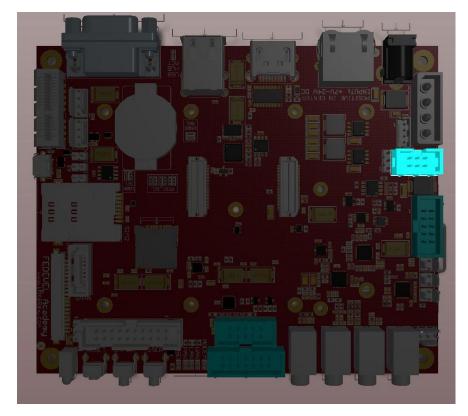

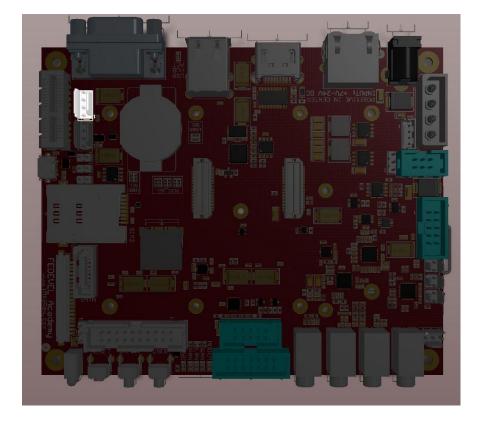

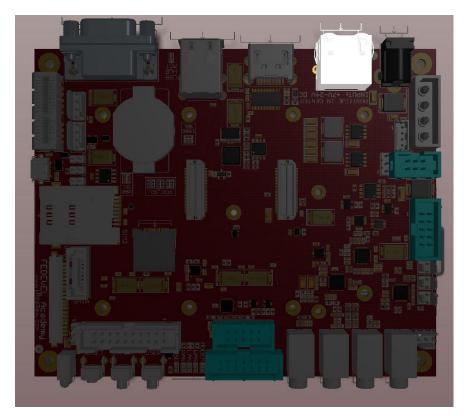

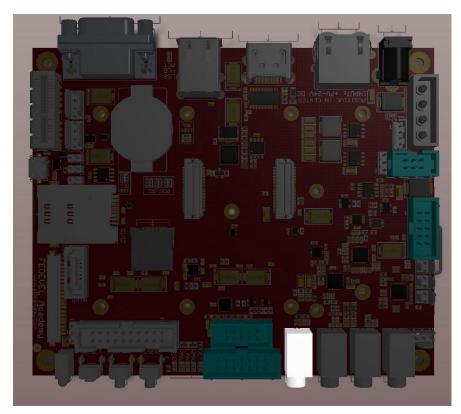

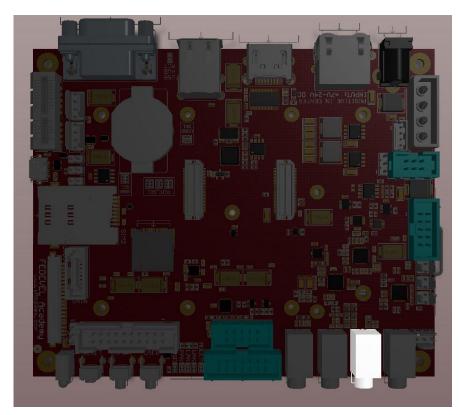

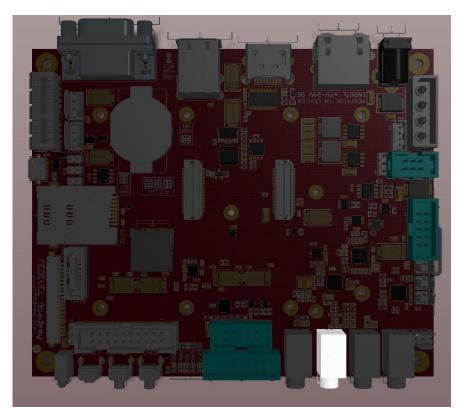

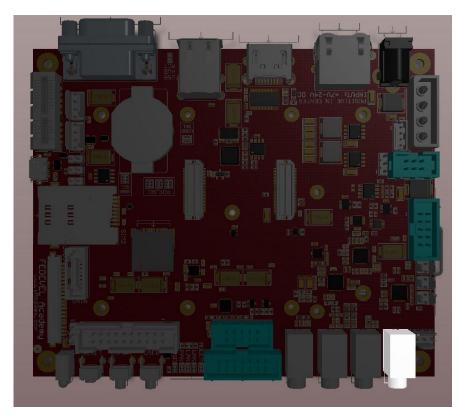

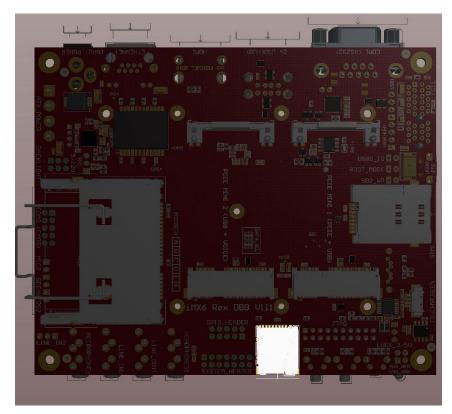

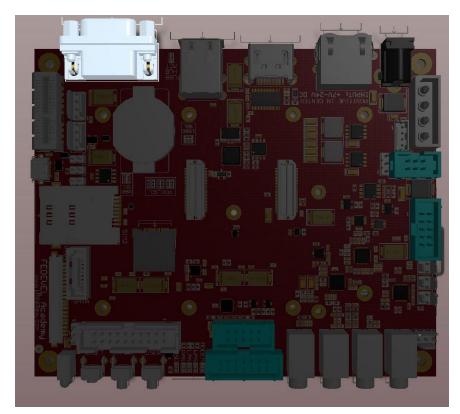

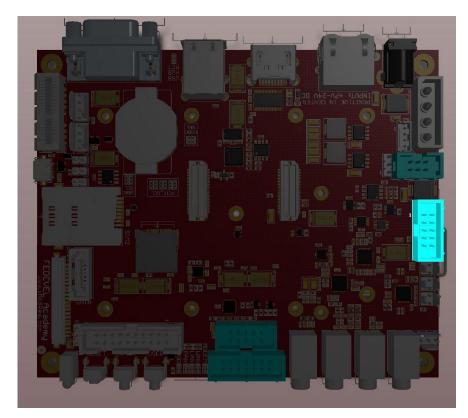

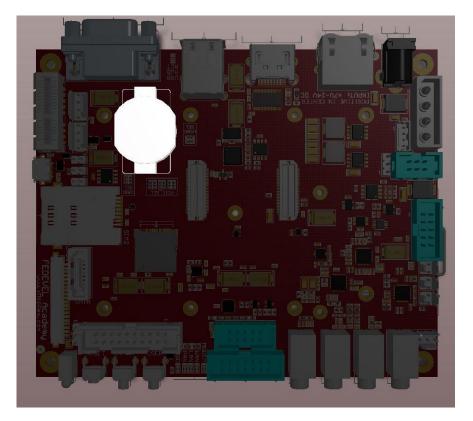

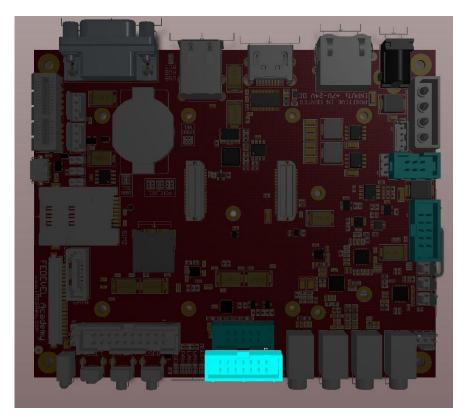

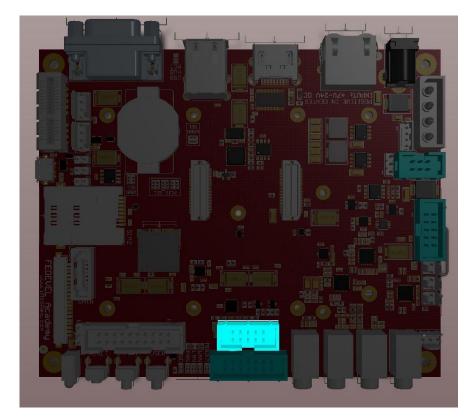

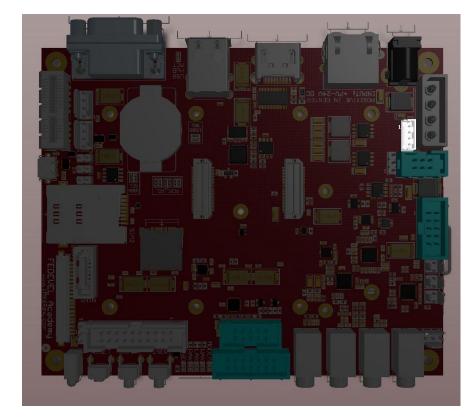

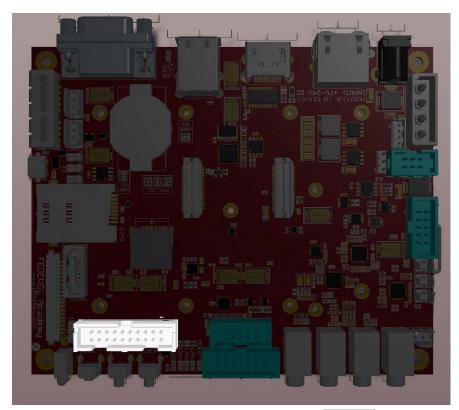

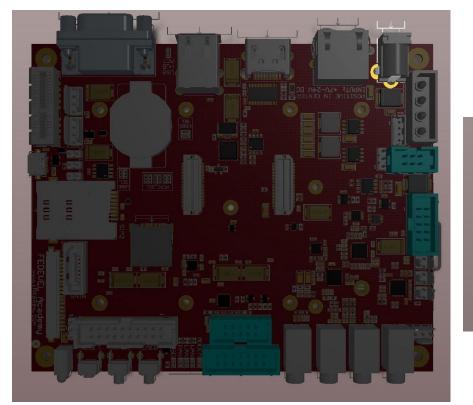

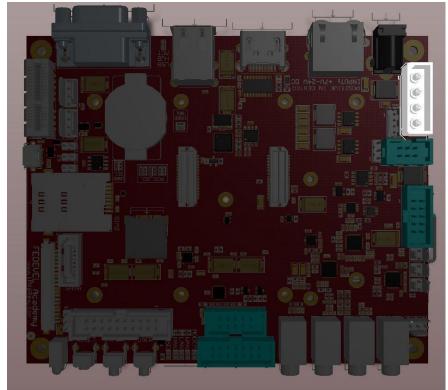

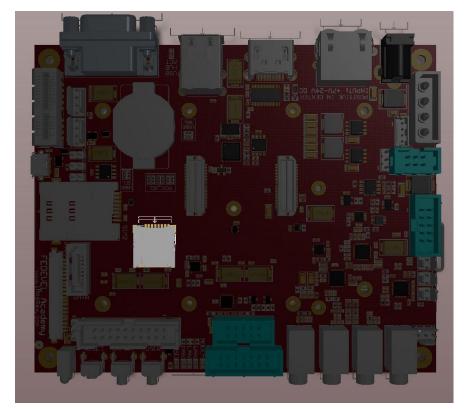

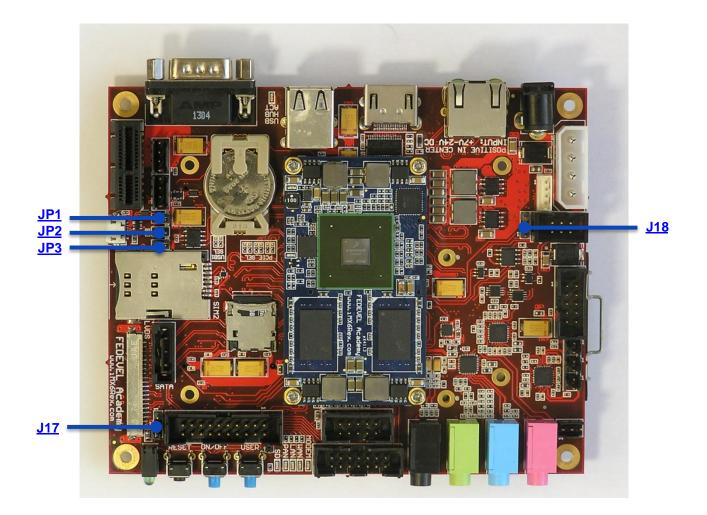

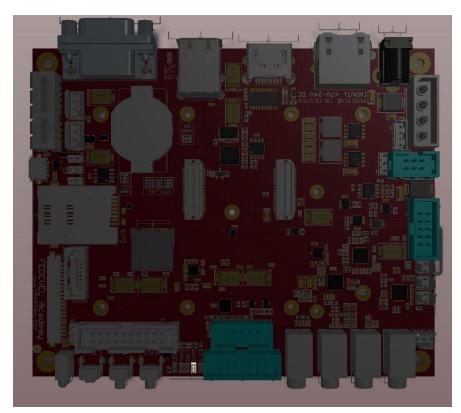

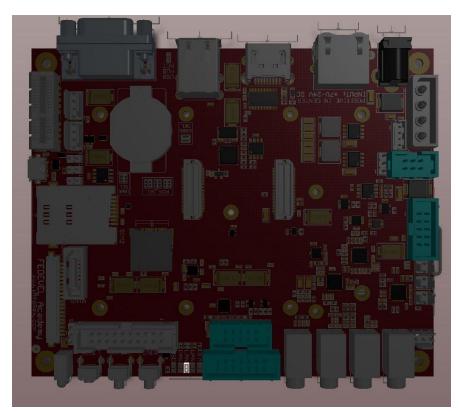

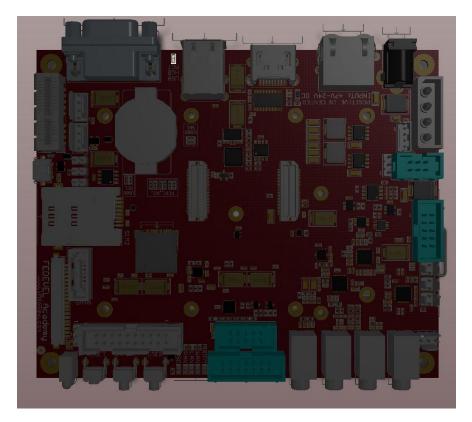

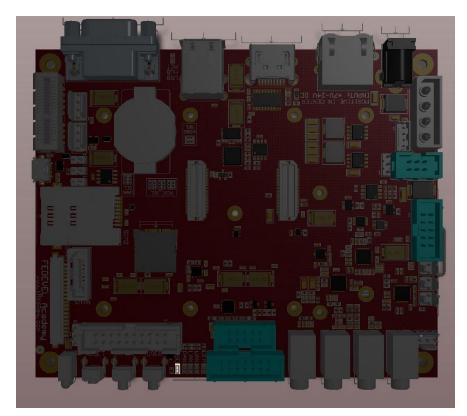

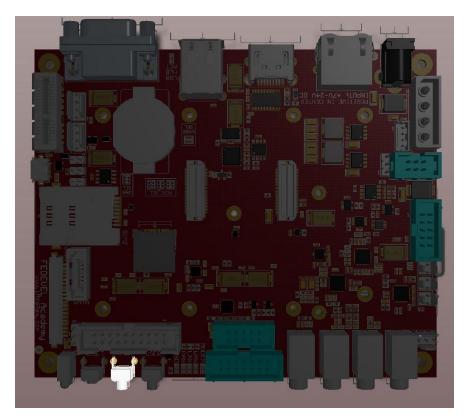

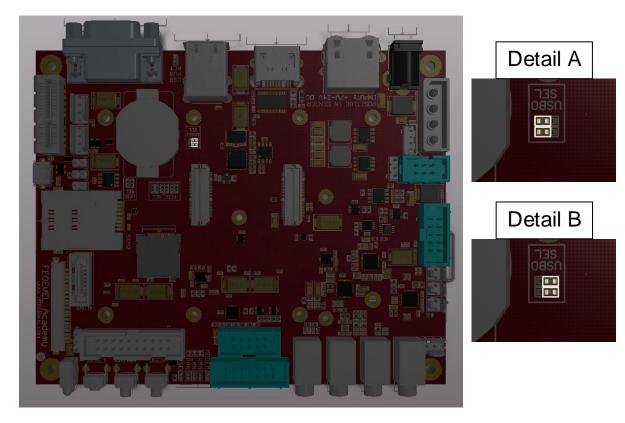

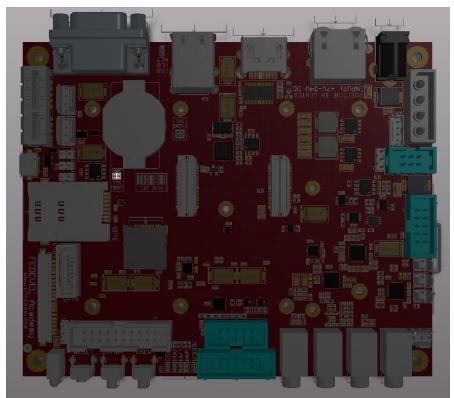

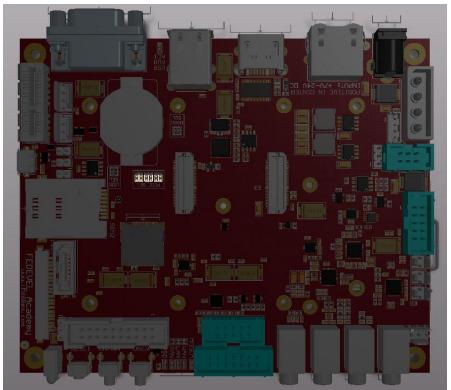

# **Connectors - Top**

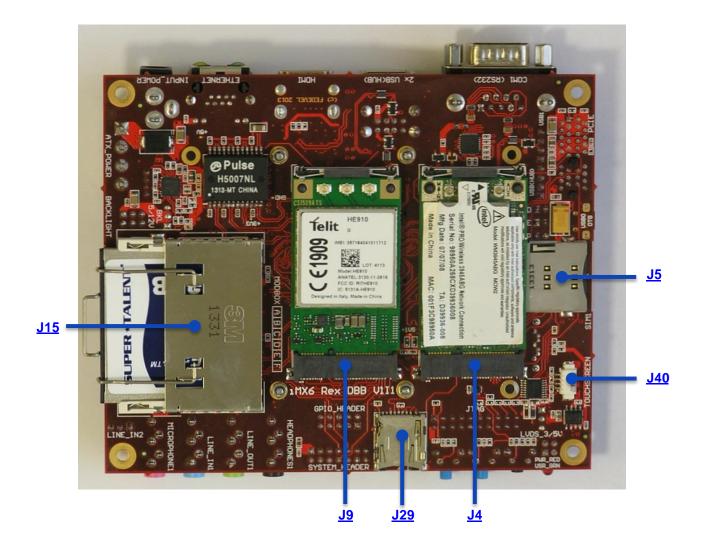

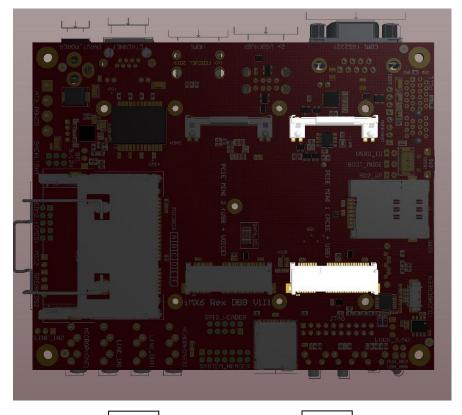

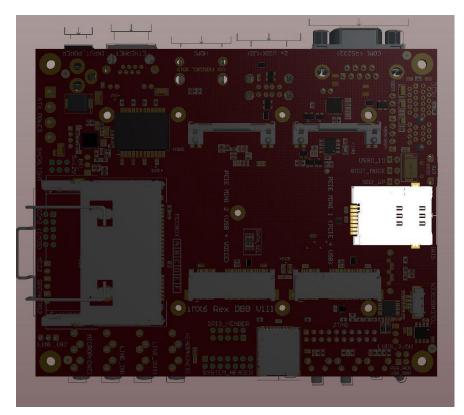

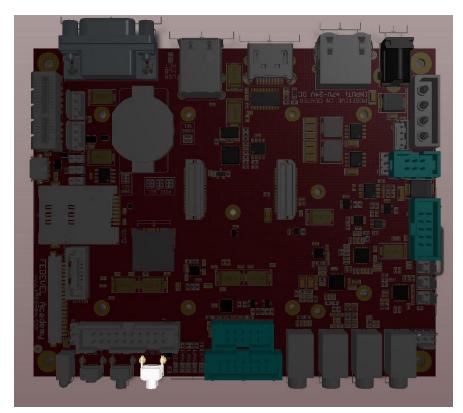

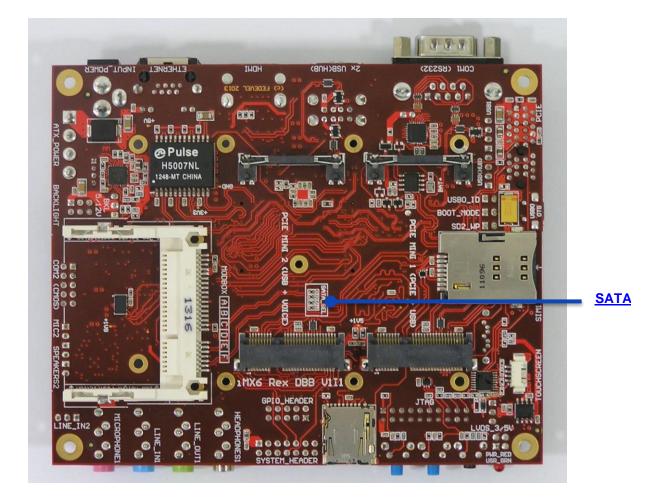

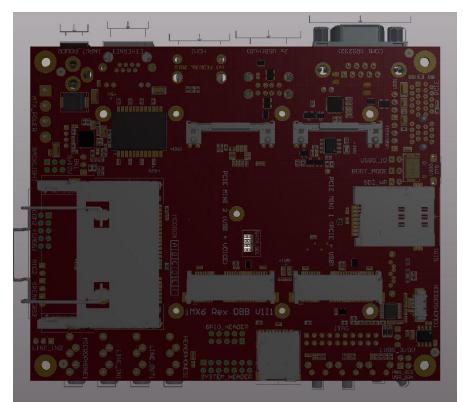

## **Connectors - Bottom**

| Ref. Number | Function                                       | Page |  |  |  |

|-------------|------------------------------------------------|------|--|--|--|

| <u>J1</u>   | Module Board to board connector                | 13   |  |  |  |

| <u>J2</u>   | Module Board to board connector (Optional)     | 15   |  |  |  |

| <u>J3</u>   | PCI Express x1 slot (Optional)                 | 17   |  |  |  |

| <u>J4</u>   | PCI Express Mini Card 1 socket                 | 19   |  |  |  |

| <u>J5</u>   | SIM Card Holder 1                              | 21   |  |  |  |

| <u>J7</u>   | SIM Card Holder 2                              | 22   |  |  |  |

| <u>J9</u>   | PCI Express Mini Card 2 socket                 | 23   |  |  |  |

| <u>J10</u>  | Speaker 2 Left                                 | 25   |  |  |  |

| <u>J11</u>  | Microphone 2                                   | 26   |  |  |  |

| <u>J12</u>  | Speaker 2 Right                                | 27   |  |  |  |

| <u>J13</u>  | Line In 2                                      | 28   |  |  |  |

| <u>J14</u>  | SATA (Optional)                                | 29   |  |  |  |

| <u>J15</u>  | CFAST Socket                                   | 30   |  |  |  |

| <u>J16</u>  | HDMI                                           | 32   |  |  |  |

| <u>J19</u>  | Backlight                                      | 34   |  |  |  |

| <u>J20</u>  | CPU-USB1 Host Header (Optional)                | 35   |  |  |  |

| <u>J21</u>  | CPU-USB0 Host / Slave Micro AB (Optional) 36   |      |  |  |  |

| <u>J22</u>  | USB 2x Host Stacked (CPU-USB0 through USB hub) | 37   |  |  |  |

| <u>J23</u>  | USB Host Header (CPU-USB0 through USB hub)     | 38   |  |  |  |

| <u>J24</u>  | Ethernet                                       | 39   |  |  |  |

| <u>J25</u>  | Headphones 1                                   | 41   |  |  |  |

| <u>J26</u>  | Line In 1                                      | 42   |  |  |  |

| <u>J27</u>  | Line Out 1                                     | 43   |  |  |  |

| <u>J28</u>  | Microphone 1                                   | 44   |  |  |  |

| <u>J29</u>  | Micro SD Slot 1                                | 45   |  |  |  |

| <u>J30</u>  | RS232                                          | 46   |  |  |  |

| <u>J31</u>  | COM2 (CMOS UART)                               | 47   |  |  |  |

| <u>J32</u>  | Battery                                        | 48   |  |  |  |

| <u>J33</u>  | System header                                  | 49   |  |  |  |

| <u>J34</u>  | GPIO header                                    | 51   |  |  |  |

| <u>J35</u>  | Power +5V Out                                  | 52   |  |  |  |

| <u>J36</u>  | JTAG                                           | 53   |  |  |  |

| <u>J37</u>  | Power Input                                    | 54   |  |  |  |

| <u>J38</u>  | ATX Power Input / Output (Optional)            | 55   |  |  |  |

| <u>J39</u>  | Micro SD Slot 2                                | 56   |  |  |  |

| <u>J40</u>  | Touchscreen                                    | 57   |  |  |  |

| <u>J41</u>  | LVDS                                           | 58   |  |  |  |

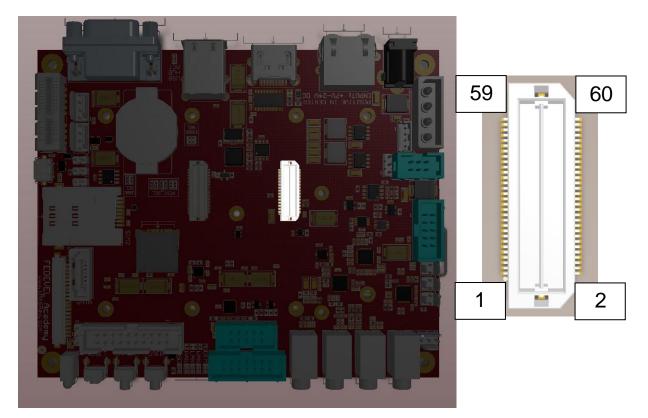

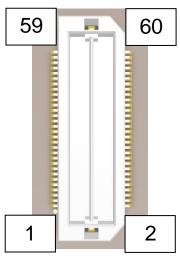

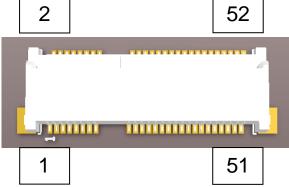

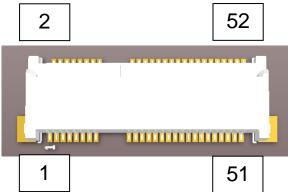

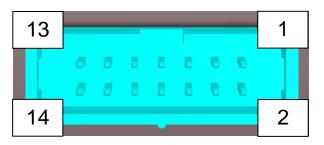

#### J1 – Module Board to Board Connector

**Description:** J1 connects the baseboard with the module. The connector contains all the important signals needed to run the board.

Connector: Samtec QTH-030-01-L-D-A

Mating: Samtec QSH-030-01-L-D-A

| Description             | Туре | Signal Name | Pin | Pin | Signal Name   | Туре | Description                                     |

|-------------------------|------|-------------|-----|-----|---------------|------|-------------------------------------------------|

| Power for the<br>Module | PO   | +Vin        | 1   | 2   | +Vin          | PO   | Power for the<br>Module                         |

| Power for the<br>Module | PO   | +Vin        | 3   | 4   | +Vin          | PO   | Power for the<br>Module                         |

| Power for the<br>Module | PO   | +Vin        | 5   | 6   | ON_OFF        | OD   | On / Off signal                                 |

| Peripheral reset        | I    | SYS_RSTn    | 7   | 8   | SYS_POKn      | 0    | Reset for the Module                            |

|                         | 0    | UART1_DSR   | 9   | 10  | UART1_RI      | 0    |                                                 |

|                         | 0    | UART1_CTS   | 11  | 12  | UART1_TXD     | I    |                                                 |

|                         | I    | UART1_RTS   | 13  | 14  | UART1_RXD     | 0    |                                                 |

|                         | I    | UART1_DTR   | 15  | 16  | UART1_DCD     | 0    |                                                 |

|                         | I    | CSPI2_CLK   | 17  | 18  | +5V_USB_VBUS  | PO   | Baseboard must<br>provide +5V<br>for the Module |

|                         | Ι    | CSPI2_CS0   | 19  | 20  | USB0_ID       | 0    | USB0 host/slave<br>mode selection               |

|                         | 0    | CSPI2_MISO  | 21  | 22  | USB0_N        | I/O  |                                                 |

|                         | I    | CSPI2_MOSI  | 23  | 24  | USB0_P        | I/O  |                                                 |

|                         | 0    | SD3_WP      | 25  | 26  | N.C.          |      |                                                 |

|                         | I    | SD3_CLK     | 27  | 28  | USB_OC        | OD   |                                                 |

|                         | I/O  | SD3_DATA0   | 29  | 30  | SD3_DATA1     | I/O  |                                                 |

|                         | I/O  | SD3_DATA2   | 31  | 32  | SD3_DATA3     | I/O  |                                                 |

|                         | I/O  | SD3_CMD     | 33  | 34  | SD3_CD        | 0    |                                                 |

| INT from<br>touchscreen | 0    | TSC_INT     | 35  | 36  | I2C2_SCL      | I    | I2C for peripherals                             |

| INT from peripherals    | OD   | CPU_INT     | 37  | 38  | I2C2_SDA      | I/O  | I2C for peripherals                             |

|                         | I    | HDMI_D0_N   | 39  | 40  | HDMI_D2_N     | I    |                                                 |

|                         | I    | HDMI_D0_P   | 41  | 42  | HDMI_D2_P     | 1    |                                                 |

|                         | 0    | HDMI_HPD    | 43  | 44  | HDMI_CEC_IN   | I/O  |                                                 |

|                         | I    | HDMI_CLK_N  | 45  | 46  | HDMI_D1_N     | 1    |                                                 |

|                         | I    | HDMI_CLK_P  | 47  | 48  | HDMI_D1_P     | I    |                                                 |

|                         |      | N.C.        | 49  | 50  | BOOT_MODE     | 0    | Open: Normal /<br>Fitted: Boots to USB          |

|                         | I/O  | TRD1_N      | 51  | 52  | TRD3_N        | I/O  |                                                 |

|                         | I/O  | TRD1_P      | 53  | 54  | TRD3_P        | I/O  |                                                 |

|                         | I    | ENET_LED_RX | 55  | 56  | ENET_LED_LINK | I    |                                                 |

|                         | I/O  | TRD0_N      | 57  | 58  | TRD2_N        | I/O  |                                                 |

|                         | I/O  | TRD0_P      | 59  | 60  | TRD2_P        | I/O  |                                                 |

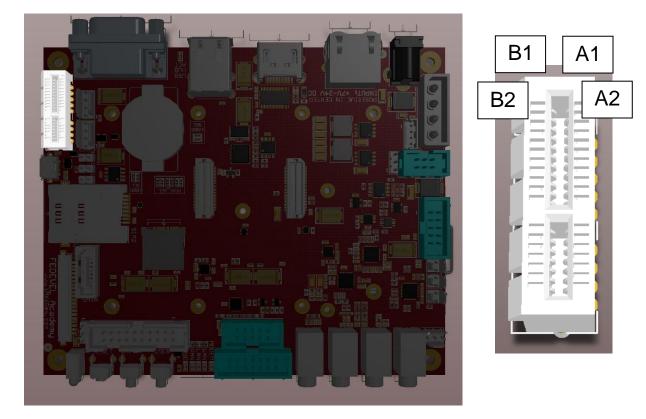

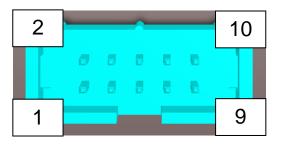

### J2 – Module Board to Board Connector (Optional)

**Description:** J2 connects the baseboard with the module. The connector contains signals, which are not required to boot the module up.

Connector: Samtec QTH-030-01-L-D-A

Mating: Samtec QSH-030-01-L-D-A

| Description        | Туре | Signal Name | Pin | Pin | Signal Name | Туре | Description             |

|--------------------|------|-------------|-----|-----|-------------|------|-------------------------|

|                    | I    | LVDS0_TX2_N | 1   | 2   | LVDS0_TX0_N | I    |                         |

|                    | I    | LVDS0_TX2_P | 3   | 4   | LVDS0_TX0_P | I    |                         |

|                    | I    | LVDS0_PWM   | 5   | 6   | LVDS0_CABC  | I    |                         |

|                    | Ι    | LVDS0_TX3_N | 7   | 8   | LVDS0_TX1_N | Ι    |                         |

|                    | I    | LVDS0_TX3_P | 9   | 10  | LVDS0_TX1_P | I    |                         |

| SD2 Activity LED   | I    | SD2_ACT     | 11  | 12  | I2C1_SDA    | I/O  | I2C for Audio           |

|                    | I    | LVDS0_CLK_N | 13  | 14  | I2C1_SCL    | I.   | I2C for Audio           |

|                    | Ι    | LVDS0_CLK_P | 15  | 16  | AUD3_TXC    | I    |                         |

| I2C on GPIO Header | I/O  | I2C3_SDA    | 17  | 18  | AUD3_TXD    | I.   |                         |

| I2C on GPIO Header | Ι    | I2C3_SCL    | 19  | 20  | AUD3_CLK    | Ι    |                         |

|                    | I/O  | SD2_CMD     | 21  | 22  | AUD3_RXD    | 0    |                         |

|                    | I/O  | SD2_DATA1   | 23  | 24  | AUD3_TXFS   | Ι    |                         |

|                    | I/O  | SD2_DATA3   | 25  | 26  | SD2_DATA0   | I/O  |                         |

|                    | I/O  | SD2_DATA5   | 27  | 28  | SD2_DATA2   | I/O  |                         |

|                    | I/O  | SD2_DATA7   | 29  | 30  | SD2_DATA4   | I/O  |                         |

|                    | 0    | UART2_CTS   | 31  | 32  | SD2_DATA6   | I/O  |                         |

|                    | I    | UART2_RTS   | 33  | 34  | SD2_WP      | 0    |                         |

|                    | 0    | UART2_RXD   | 35  | 36  | SD2_CLK     | I    |                         |

|                    | I    | UART2_TXD   | 37  | 38  | SD2_CD      | 0    |                         |

|                    | OD   | PCIE_WAKE   | 39  | 40  | USB1_N      | I/O  |                         |

|                    | 0    | JTAG_nTRST  | 41  | 42  | USB1_P      | I/O  |                         |

|                    | 0    | JTAG_TCK    | 43  | 44  | USB1_PWR_EN | I    |                         |

|                    | I    | JTAG_TDO    | 45  | 46  | CLK1_N      | I.   | Clock for PCle          |

|                    | 0    | JTAG_TDI    | 47  | 48  | CLK1_P      | I    | Clock for PCIe          |

|                    | 0    | JTAG_TMS    | 49  | 50  | +3V3_MODULE | PI   | +3V3 from the<br>Module |

|                    | I    | PCIE_TX_N   | 51  | 52  | PCIE_RX_N   | 0    |                         |

|                    | I    | PCIE_TX_P   | 53  | 54  | PCIE_RX_P   | 0    |                         |

|                    | G    | GND         | 55  | 56  | GND         | G    |                         |

|                    | I    | SATA_TX_N   | 57  | 58  | SATA_RX_N   | 0    |                         |

|                    | I    | SATA_TX_P   | 59  | 60  | SATA_RX_P   | 0    |                         |

# J3 – PCI Express x1 Slot (Optional)

**Description:** PCI Express can be optionally redirected to the J3 PCIE slot (requires resistor swapping, see the schematic). To supply +12V, the ATX connector must be used (<u>J38</u>)

Connector: FCI 10018783-10010TLF

| Description              | Туре | Pin Name | Pin       | Pin        | Pin Name | Туре | Description              |

|--------------------------|------|----------|-----------|------------|----------|------|--------------------------|

| Hot-Plug presence detect | 0    | PRSNT1#  | A1        | B1         | +12V_1   | PO   |                          |

|                          | PO   | +12V_4   | A2        | B2         | +12V_2   | PO   |                          |

|                          | PO   | +12V_5   | A3        | <b>B</b> 3 | +12V_3   | PO   |                          |

|                          | G    | GND_6    | A4        | <b>B</b> 4 | GND_1    | G    |                          |

| Not connected            |      | JTAG2    | A5        | B5         | SMCLK    | 0    | Connected to I2C2        |

| Not connected            |      | JTAG3    | A6        | <b>B6</b>  | SMDAT    | I/O  | Connected to I2C2        |

| Not connected            |      | JTAG4    | A7        | B7         | GND_2    | G    |                          |

| Not connected            |      | JTAG5    | <b>A8</b> | <b>B</b> 8 | +3.3V_1  | PO   |                          |

|                          | PO   | +3.3V_2  | A9        | <b>B</b> 9 | JTAG1    |      | Not connected            |

|                          | PO   | +3.3V_3  | A10       | B10        | 3.3VAUX  | PO   | Connected to +3V3        |

| Fundamental reset        | 0    | PERST#   | A11       | B11        | WAKE#    | OD   | PCIe Wake up             |

|                          |      | Μ        | lechan    | ical K     | еу       |      |                          |

|                          | G    | GND_7    | A12       | B12        | RSVD     |      |                          |

| PCIe Clock Positive      | 0    | REFCLK+  | A13       | B13        | GND_3    | G    |                          |

| PCIe Clock Negative      | 0    | REFCLK-  | A14       | B14        | PET_P0   | 0    | PCIe Transmit Positive   |

|                          | G    | GND_8    | A15       | B15        | PET_N0   | 0    | PCIe Transmit Negative   |

| PCIe Receive Positive    | I    | PER_P0   | A16       | B16        | GND_4    | G    |                          |

| PCIe Receive Negative    | I    | PER_N0   | A17       | B17        | PRSNT2#  | I    | Hot-Plug presence detect |

|                          | G    | GND_9    | A18       | B18        | GND_5    | G    |                          |

# J4 – PCI Express Mini Card 1 socket

**Description:** J4 is connected to the PCI Express and USB1 interface. SIM Card ( $\underline{J5}$ ) functionality is also supported.

Connector: JAE MM60-52B1-E1-R650

Card Latch: JAE MM60-EZH059-B5-R650

| Description            | Туре | Pin Name            | Pin | Pin | Pin Name   | Туре | Description         |

|------------------------|------|---------------------|-----|-----|------------|------|---------------------|

| PCIe Wake up           | OD   | WAKE#               | 1   | 2   | 3.3V_1     | PO   |                     |

|                        |      | Reserved_1          | 3   | 4   | GND_7      | G    |                     |

|                        |      | Reserved_2          | 5   | 6   | 1.5V_1     | PO   |                     |

| Not connected          |      | CLKREQ#             | 7   | 8   | UIM_PWR    | PI   | SIM Card Power      |

|                        | G    | GND_1               | 9   | 10  | UIM_DATA   | I/O  | SIM Card Data       |

| PCIe Clock Negative    | 0    | REFCLK-             | 11  | 12  | UIM_CLK    | I    | SIM Card Clock      |

| PCIe Clock Positive    | 0    | REFCLK+             | 13  | 14  | UIM_RESET  | 1    | SIM Card Reset      |

|                        | G    | GND_2               | 15  | 16  | UIM_VPP    | PI   | SIM Card VPP        |

|                        |      |                     |     |     |            |      |                     |

| Not connected          |      | Reserved/<br>UIM_C8 | 17  | 18  | GND_8      | G    |                     |

| Not connected          |      | Reserved/<br>UIM_C4 | 19  | 20  | W_DISABLE# | 0    | Wireless disable    |

|                        | G    | GND_3               | 21  | 22  | PERST#     | 0    | Reset               |

| PCIe Receive Negative  | I    | PERn0               | 23  | 24  | +3.3Vaux   | PO   | Connected to +3V3   |

| PCIe Receive Positive  | I    | PERp0               | 25  | 26  | GND_9      | G    |                     |

|                        | G    | GND_4               | 27  | 28  | 1.5V_2     | PO   |                     |

|                        | G    | GND_5               | 29  | 30  | SMB_CLK    | 0    | Connected to I2C2   |

| PCIe Transmit Negative | 0    | PETn0               | 31  | 32  | SMB_DATA   | I/O  | Connected to I2C2   |

| PCIe Transmit Positive | 0    | PETp0               | 33  | 34  | GND_10     | G    |                     |

|                        | G    | GND_6               | 35  | 36  | USB_D-     | I/O  | Connected to USB1   |

| Connected to Ground    | G    | Reserved_3          | 37  | 38  | USB_D+     | I/O  | Connected to USB1   |

| Connected to +3.3V     | PO   | Reserved_4          | 39  | 40  | GND_11     | G    |                     |

| Connected to +3.3V     | PO   | Reserved_5          | 41  | 42  | LED_WWAN#  | I    | Status indicator D1 |

| Connected to Ground    | G    | Reserved_6          | 43  | 44  | LED_WLAN#  | I    | Status indicator D2 |

| Not connected          |      | Reserved_7          | 45  | 46  | LED_WPAN#  | I    | Status indicator D3 |

| Not connected          |      | Reserved_8          | 47  | 48  | 1.5V_3     | PO   |                     |

| Not connected          |      | Reserved_9          | 49  | 50  | GND_12     | G    |                     |

| Not connected          |      | Reserved_10         | 51  | 52  | 3.3V_2     | PO   |                     |

|                        |      |                     |     |     |            |      |                     |

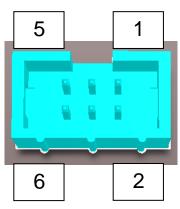

# J5 – SIM Card Holder 1

**Description:** J5 is a SIM Card socket connected to the PCI Express Mini Card 1 (J4).

Socket: Molex 0475531001

| Pin | Pin Name | Туре | Description    |

|-----|----------|------|----------------|

| C1  | VCC      | PO   | SIM Card Power |

| C2  | RESET    | 0    | SIM Card Reset |

| C3  | CLK      | 0    | SIM Card Clock |

| C5  | GND      | G    |                |

| C6  | VPP      | PO   | SIM Card VPP   |

| C7  | I/O      | I/O  | SIM Card Data  |

| S1  | S1       |      | Not connected  |

| S2  | S2       |      | Not connected  |

# J7 – SIM Card Holder 2

**Description:** J7 is a SIM Card socket connected to the PCI Express Mini Card 2 (<u>J9</u>).

Socket: Molex 0475531001

| Pin        | Pin Name | Туре | Description    |

|------------|----------|------|----------------|

| C1         | VCC      | PO   | SIM Card Power |

| C2         | RESET    | 0    | SIM Card Reset |

| C3         | CLK      | 0    | SIM Card Clock |

| C5         | GND      | G    |                |

| C6         | VPP      | PO   | SIM Card VPP   |

| C7         | I/O      | I/O  | SIM Card Data  |

| <b>S</b> 1 | S1       |      | Not connected  |

| S2         | S2       |      | Not connected  |

#### J9 – PCI Express Mini Card 2 Connector

**Description:** J9 is connected to the USB0 Hub interface. Connector also provides an audio support (Audio2) and the SIM Card functionality (<u>J7</u>). Connector J9 is intended to use for wireless modems. This connector is not connected to any PCIE interface.

Connector: JAE MM60-52B1-E1-R650

Card Latch: JAE MM60-EZH059-B5-R650

| Description          | Туре | Pin Name            | Pin | Pin | Pin Name   | Туре | Description                       |

|----------------------|------|---------------------|-----|-----|------------|------|-----------------------------------|

| Connected to CPU_INT | OD   | WAKE#               | 1   | 2   | 3.3V_1     | PO   |                                   |

|                      |      | Reserved_1          | 3   | 4   | GND_7      | G    |                                   |

|                      |      | Reserved_2          | 5   | 6   | 1.5V_1     | PO   |                                   |

| Not connected        |      | CLKREQ#             | 7   | 8   | UIM_PWR    | PI   | SIM Card Power                    |

|                      | G    | GND_1               | 9   | 10  | UIM_DATA   | I/O  | SIM Card Data                     |

| Not connected        |      | REFCLK-             | 11  | 12  | UIM_CLK    | I    | SIM Card Clock                    |

| Not connected        |      | REFCLK+             | 13  | 14  | UIM_RESET  | I    | SIM Card Reset                    |

|                      | G    | GND_2               | 15  | 16  | UIM_VPP    | PI   | SIM Card VPP                      |

|                      |      |                     |     |     |            |      |                                   |

| Not connected        |      | Reserved/<br>UIM_C8 | 17  | 18  | GND_8      | G    |                                   |

| Not connected        |      | Reserved/<br>UIM_C4 | 19  | 20  | W_DISABLE# | 0    | Wireless disable                  |

|                      | G    | GND_3               | 21  | 22  | PERST#     | 0    | Reset                             |

| Not connected        |      | PERn0               | 23  | 24  | +3.3Vaux   | PO   | Connected to +3V3                 |

| Not connected        |      | PERp0               | 25  | 26  | GND_9      | G    |                                   |

|                      | G    | GND_4               | 27  | 28  | 1.5V_2     | PO   |                                   |

|                      | G    | GND_5               | 29  | 30  | SMB_CLK    | 0    | Connected to I2C2                 |

| Not connected        |      | PETn0               | 31  | 32  | SMB_DATA   | I/O  | Connected to I2C2                 |

| Not connected        |      | PETp0               | 33  | 34  | GND_10     | G    |                                   |

|                      | G    | GND_6               | 35  | 36  | USB_D-     | I/O  | Connected to USB0<br>Downstream 4 |

| Connected to Ground  | G    | Reserved_3          | 37  | 38  | USB_D+     | I/O  | Connected to USB0<br>Downstream 4 |

| Connected to +3.3V   | PO   | Reserved_4          | 39  | 40  | GND_11     | G    |                                   |

| Connected to +3.3V   | PO   | Reserved_5          | 41  | 42  | LED_WWAN#  | I    |                                   |

| Connected to Ground  | G    | Reserved_6          | 43  | 44  | LED_WLAN#  |      | Not connected                     |

| Audio2 Clock         | I/O  | Reserved_7          | 45  | 46  | LED_WPAN#  |      | Not connected                     |

| Audio2 RX            | 0    | Reserved_8          | 47  | 48  | 1.5V_3     | PO   |                                   |

| Audio2 TX            | I    | Reserved_9          | 49  | 50  | GND_12     | G    |                                   |

| Audio2 Sync          | I/O  | Reserved_10         | 51  | 52  | 3.3V_2     | PO   |                                   |

|                      |      |                     |     |     |            |      |                                   |

#### J10 – Speaker 2 Left Header

**Description:** J10 is connected to the Left Channel Speakers Output of the Modern Audio Interface (Audio2). The speaker output mode can be selected between: differential (default build option) or single-ended. When differential mode is used, this speaker output signal is amplified.

Connector: FCI 76384-302LF

Mating housing: FCI 65240-002LF or equivalent

Mating crimps: FCI 76347-401LF or equivalent

#### Differential mode:

| Pin | Signal Name | Туре | Description                      |

|-----|-------------|------|----------------------------------|

| 1   | MODEM_LOUT+ | 0    | Speakers 2 Left Channel Positive |

| 2   | MODEM_LOUT- | 0    | Speakers 2 Left Channel Negative |

#### Single-ended mode:

| Pin | Signal Name | Туре | Description             |

|-----|-------------|------|-------------------------|

| 1   | MODEM_LOUT+ | 0    | Speakers 2 Left Channel |

| 2   | MODEM_LOUT- | G    | Signal ground           |

## J11 – Microphone 2 Header

**Description:** An external microphone can be connected to the modern Audio 2 via J11. The microphone input supplies bias voltage.

Connector: FCI 76384-302LF

Mating housing: FCI 65240-002LF or equivalent

Mating crimps: FCI 76347-401LF or equivalent

| Pin | Signal Name     | Туре | Description        |

|-----|-----------------|------|--------------------|

| 1   | AUD2_FIL_MIC_IN | I    | Microphone 2 Input |

| 2   | GND             | G    | Signal ground      |

#### J12 – Speaker 2 Right Header

**Description:** J12 is connected to the Right Channel Speakers Output of the Modern Audio Interface (Audio2). The speaker output mode can be selected between: differential (default build option) or single-ended. When differential mode is used, this speaker output signal is amplified.

Connector: FCI 76384-302LF

Mating housing: FCI 65240-002LF or equivalent

Mating crimps: FCI 76347-401LF or equivalent

**Differential mode:**

| Pin | Signal Name | Туре | Description                       |

|-----|-------------|------|-----------------------------------|

| 1   | MODEM_ROUT+ | 0    | Speakers 2 Right Channel Positive |

| 2   | MODEM_ROUT- | 0    | Speakers 2 Right Channel Negative |

#### Single-ended mode:

| Pin | Signal Name | Туре | Description              |

|-----|-------------|------|--------------------------|

| 1   | MODEM_ROUT+ | 0    | Speakers 2 Right Channel |

| 2   | MODEM_ROUT- | G    | Signal ground            |

# J13 – Line Input 2 Header

**Description:** J13 is connected to the Modern Audio Interface (Audio2) Line Input.

Connector: FCI 76384-303LF

Mating housing: FCI 65240-003LF or equivalent

Mating crimps: FCI 76347-401LF or equivalent

| Pin | Signal Name | Туре | Description        |

|-----|-------------|------|--------------------|

| 1   | LINE_IN_C_R | 1    | Right Line Input 2 |

| 2   | GND         | G    | Signal ground      |

| 3   | LINE_IN_C_L | I    | Left Line Input 2  |

# J14 – SATA Connector (Optional)

**Description:** J14 can be optionally connected to the SATA Interface (see schematic, resistor swap is required).

#### Connector: Molex 0471554001

| Pin | Pin Name | Туре | Description                   |

|-----|----------|------|-------------------------------|

| 1   | GND1     | G    |                               |

| 2   | TX+      | 0    | SATA Transmit Positive Signal |

| 3   | TX-      | 0    | SATA Transmit Negative Signal |

| 4   | GND2     | G    |                               |

| 5   | RX-      | Ι    | SATA Receive Negative Signal  |

| 6   | RX+      | I    | SATA Receive Positive Signal  |

| 7   | GND3     | G    |                               |

# J15 – CFAST Socket

**Description:** J15 provides support for the removable SATA SSD devices. For rugged environment there is an option to use a locking mechanism.

Connector: 3M N7G24-A0B2RB-10-0HT

Locking mechanism: 3M 7E50-C016-00 (Optional)

| Pin        | Pin Name      | Туре | Description                         |

|------------|---------------|------|-------------------------------------|

| S1         | SGND          | G    |                                     |

| S2         | A+ (Host TX+) | 0    | SATA Transmit Positive Signal       |

| S3         | A- (Host TX-) | 0    | SATA Transmit Negative Signal       |

| <b>S</b> 4 | SGND          | G    |                                     |

| S5         | B- (Host RX-) | 1    | SATA Receive Negative Signal        |

| S6         | B+ (Host RX+) | I    | SATA Receive Positive Signal        |

| S7         | SGND          | G    |                                     |

|            |               |      |                                     |

| PC1        | CDI           | I/O  | Card detection / Sleep mode control |

| PC2        | GND           | G    |                                     |

| PC3        | TBD           |      | Not connected                       |

| PC4        | TBD           |      | Not connected                       |

| PC5        | TBD           |      | Not connected                       |

| PC6        | TBD           |      | Not connected                       |

| PC7        | GND           | G    |                                     |

| PC8        | LED1          |      | Not connected                       |

| PC9        | LED2          |      | Not connected                       |

| PC10       | IO1           |      | Not connected                       |

| PC11       | 102           |      | Not connected                       |

| PC12       | IO3           |      | Not connected                       |

| PC13       | 3.3V          | PO   | +3.3V supply for the device         |

| PC14       | 3.3V          | PO   | +3.3V supply for the device         |

| PC15       | PGND          | G    |                                     |

| PC16       | PGND          | G    |                                     |

| PC17       | CDO           | 0    | Card detection                      |

|            |               |      |                                     |

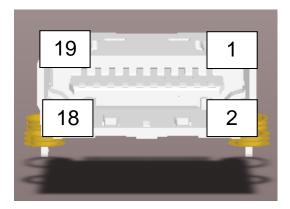

# J16 – HDMI Connector

Description: J16 is connected to the HDMI interface.

#### Connector: Molex 47151-0001

| Pin | Pin Name  | Туре | Description                  |

|-----|-----------|------|------------------------------|

| 1   | D2+       | 0    | TMDS Data2+                  |

| 2   | D2 SHIELD | G    | TMDS Data2 Shield            |

| 3   | D2-       | 0    | TMDS Data2-                  |

| 4   | D1+       | 0    | TMDS Data1+                  |

| 5   | D1 SHIELD | G    | TMDS Data1 Shield            |

| 6   | D1-       | 0    | TMDS Data1-                  |

| 7   | D0+       | 0    | TMDS Data0+                  |

| 8   | D0 SHIELD | G    | TMDS Data0 Shield            |

| 9   | D0-       | 0    | TMDS Data0-                  |

| 10  | CK+       | 0    | TMDS Clock+                  |

| 11  | CK SHIELD | G    | TMDS Clock Shield            |

| 12  | CK-       | 0    | TMDS Clock-                  |

| 13  | CE REMOTE | I/O  | Consumer Electronics Control |

| 14  | NC.14     |      | Not connected                |

| 15  | DDC CLK   | 0    | Connected to I2C2            |

| 16  | DDC DATA  | I/O  | Connected to I2C2            |

| 17  | GND       | G    |                              |

| 18  | +5V       | PO   | +3.3V Supply for the device  |

| 19  | HP DET    | I    | Hot Plug detect              |

## J19 – Backlight Header

**Description:** J19 provides a backlight support for the LVDS display (J41). This connector contains also a brightness regulation and the Content-Adaptive Backlight Control (CABC). Supply voltage for a backlight can be selected by jumper J18 (between +5V or +12V, for +12V the ATX connector must be used).

#### Connector: 3M 30306-6002HB

Mating housing: FCI 71600-006LF or equivalent

| Description                               | Туре | Signal Name    | Pin | Pin | Signal Name | Туре | Description           |

|-------------------------------------------|------|----------------|-----|-----|-------------|------|-----------------------|

| Supply for the<br>backlight<br>+5V / +12V | PO   | +BKLT_VCC      | 1   | 2   | GND         | G    |                       |

| Backlight enable                          | 0    | P_ENABKL_5V    | 3   | 4   | BKLT_ADJ    | 0    | Brightness regulation |

| LVDS CABC<br>control                      | 0    | BUF_LVDS0_CABC | 5   | 6   | N.C.        |      |                       |

# J20 – CPU-USB1 Header (Optional)

**Description:** J20 is a header for the CPU-USB1 Interface. To use this header, resistor swap is required. See the schematic.

Connector: FCI 76384-304LF

Mating housing: FCI 65240-004LF or equivalent

Mating crimps: FCI 76347-401LF or equivalent

| Pin | Signal Name   | Туре | Description               |

|-----|---------------|------|---------------------------|

| 1   | +5V_USB1_VBUS | PO   | +5V supply for the device |

| 2   | USB1_CON_N    | I/O  | CPU-USB1 Negative signal  |

| 3   | USB1_CON_P    | I/O  | CPU-USB1 Positive signal  |

| 4   | GND           | G    |                           |

www.iMX6Rex.com

## J21 – CPU-USB0 Micro AB (Optional)

**Description:** J21 is connected to the CPU-USB0 Interface. ID selection (defines USB0 as a host or as a slave) can be chosen by the jumper JP1. Connector is intended to use as a slave for the debugging purposes. To use this connector, resistor swap is required. See the schematic.

#### Connector: Molex 0475890001

| Pin | Signal Name | Туре | Description          |

|-----|-------------|------|----------------------|

| 1   | +5V_USB_OTG | PO   | Not connected        |

| 2   | USB1_CON_N  | I/O  | USB0 Negative signal |

| 3   | USB1_CON_P  | I/O  | USB0 Positive signal |

| 4   | USB0_ID     | I/O  | USB0 Host Selection  |

| 5   | GND         | G    |                      |

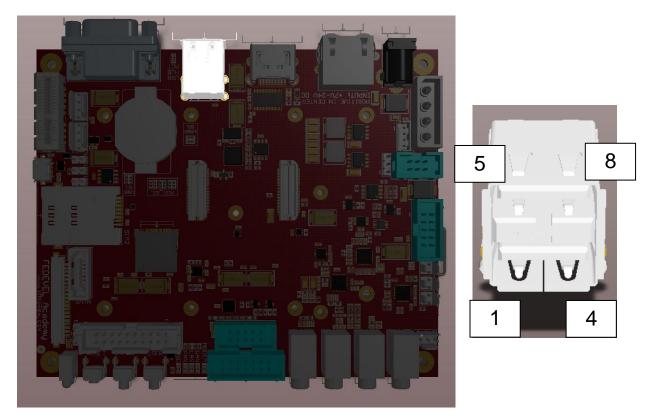

### J22 – USB Stacked A Connector

**Description:** J22 is connected to the USB Hub located on the baseboard. This on board USB hub connects to the CPU-USB0.

**Connector:** TE 5787617-1

| Description                             | Туре | Signal Name    | Pin | Pin | Signal Name     | Туре | Description                             |

|-----------------------------------------|------|----------------|-----|-----|-----------------|------|-----------------------------------------|

| +5V supply for the device               | PO + | 5V_USBDN1_VBUS | 1   | 5   | +5V_USBDN2_VBUS | PO   | +5V supply for<br>the device            |

| USB0<br>Downstream 1<br>Negative signal | I/O  | USBDN1_CON_N   | 2   | 6   | USBDN2_CON_N    | I/O  | USB0<br>Downstream 2<br>Negative signal |

| USB0<br>Downstream 1<br>Positive signal | I/O  | USBDN1_CON_P   | 3   | 7   | USBDN2_CON_P    | I/O  | USB0<br>Downstream 2<br>Positive signal |

|                                         | G    | GND            | 4   | 8   | GND             | G    |                                         |

#### J23 – USB0 Header

**Description:** J23 is connected to the USB Hub located on the baseboard. This on board USB hub connects to the CPU-USB0.

Connector: FCI 76384-304LF

Mating housing: FCI 65240-004LF or equivalent

Mating crimps: FCI 76347-401LF or equivalent

| Pin | Signal Name     | Туре | Description                           |

|-----|-----------------|------|---------------------------------------|

| 1   | +5V_USBDN3_VBUS | PO   | +5V supply for the device             |

| 2   | USBDN3_CON_N    | I/O  | USB0 Hub Downstream 3 Negative signal |

| 3   | USBDN3_CON_P    | I/O  | USB0 Hub Downstream 3 Positive signal |

| 4   | GND             | G    |                                       |

### J24 – Ethernet Connector

**Description:** J24 is 1Gb Ethernet interface.

#### **Connector:** Tyco 2-406549-1

| Pin | Pin Name | Туре | Description          |

|-----|----------|------|----------------------|

| 1   | BI_DA+   | I/O  | TRD0 Positive signal |

| 2   | BI_DA-   | I/O  | TRD0 Negative signal |

| 3   | BI_DB+   | I/O  | TRD1 Positive signal |

| 4   | BI_DC+   | I/O  | TRD2 Positive signal |

| 5   | BI_DC-   | I/O  | TRD2 Negative signal |

| 6   | BI_DB-   | I/O  | TRD1 Negative signal |

| 7   | BI_DD+   | I/O  | TRD3 Positive signal |

| 8   | BI_DD-   | I/O  | TRD3 Negative signal |

#### **LED Function:**

| Link / Activity         | State of yellow LED | State of green LED |

|-------------------------|---------------------|--------------------|

| Link off                | OFF                 | OFF                |

| 1000 Link / No activity | ON                  | OFF                |

| 1000 Link / Activity    | Blinking            | OFF                |

| 100 Link / No Activity  | OFF                 | ON                 |

| 100 Link / Activity     | OFF                 | Blinking           |

| 10 Link / No Activity   | ON                  | ON                 |

| 10 Link / Activity      | Blinking            | Blinking           |

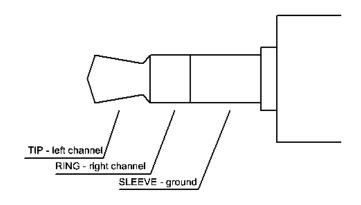

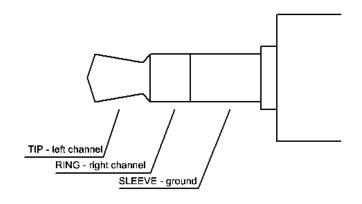

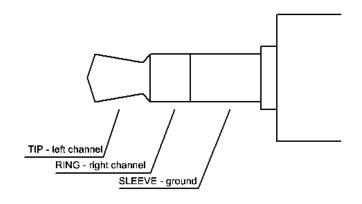

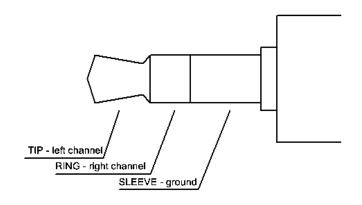

## J25 – Headphones 1 Jack

**Description:** J25 is connected to the Audio 1 Codec Headphones. Signal can be amplified if required.

#### Connector: CUI SJ1-3535NG

| Pin | Pin Name | Signal Name | Туре | Description                |

|-----|----------|-------------|------|----------------------------|

| 1   | sleeve   | GND         | G    |                            |

| 2   | tip      | FIL_HP_OUTL | 0    | Headphones 1 Left Channel  |

| 3   | ring     | FIL_HP_OUTR | 0    | Headphones 1 Right Channel |

## J26 – Line In 1 Jack

**Description:** J26 is connected to the Audio 1 Codec Line Input.

#### Connector: CUI SJ1-3535NG-BE

| Pin | Pin Name | Signal Name  | Туре | Description                |

|-----|----------|--------------|------|----------------------------|

| 1   | sleeve   | GND          | G    |                            |

| 2   | tip      | FIL_LINEIN_L | I    | Line Input 1 Left Channel  |

| 3   | ring     | FIL_LINEIN_R | I    | Line Input 1 Right Channel |

## J27 – Line Out 1 Jack

**Description:** J27 is connected to the Audio 1 Codec Line Output.

#### Connector: CUI SJ1-3535NG-GR

| Pin | Pin Name | Signal Name   | Туре | Description                 |

|-----|----------|---------------|------|-----------------------------|

| 1   | sleeve   | GND           | G    |                             |

| 2   | tip      | FIL_AUD_OUT_L | 0    | Line Output 1 Left Channel  |

| 3   | ring     | FIL_AUD_OUT_R | 0    | Line Output 1 Right Channel |

# J28 – Microphone 1 Jack

**Description:** J28 is connected to the Audio 1 Microphone input.

#### Connector: CUI SJ1-3535NG-PI

| Pin | Pin Name | Signal Name | Туре | Description        |

|-----|----------|-------------|------|--------------------|

| 1   | sleeve   | GND         | G    |                    |

| 2   | tip      | FIL_MIC_IN  | I    | Microphone 1 Input |

| 3   | ring     | FIL_MIC_IN  | I    | Microphone 1 Input |

### J29 – Micro SD Slot 1

**Description:** J29 is connected to the CPU-SD3 interface. Card detection is supported. When resistor R105 is not fitted, write protection is enabled.

**Connector:** Hirose DM3AT-SF-PEJM5

| Pin | Pin Name | Туре | Description          |

|-----|----------|------|----------------------|

| 1   | DAT2     | I/O  |                      |

| 2   | CD/DAT3  | I/O  |                      |

| 3   | CMD      | I/O  |                      |

| 4   | VDD      | PO   |                      |

| 5   | CLK      | 0    |                      |

| 6   | VSS      | G    |                      |

| 7   | DAT0     | I/O  |                      |

| 8   | DAT1     | I/O  |                      |

| 9   | SW1      | I    | Card detection pin 1 |

| 11  | SW2      | I    | Card detection pin 2 |

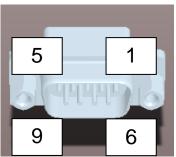

## J30 – RS232 DB9 Connector

**Description:** J30 is connected to the full COM1 serial port via a RS232 transceiver.

**Connector:** TE 1734351-1

| Pin | Signal Name   | Туре | Description |

|-----|---------------|------|-------------|

| 1   | RS232_DCD_CON | I    |             |

| 2   | RS232_RXD_CON | I    |             |

| 3   | RS232_TXD_CON | 0    |             |

| 4   | RS232_DTR_CON | 0    |             |

| 5   | GND           | G    |             |

| 6   | RS232_DSR_CON | I    |             |

| 7   | RS232_RTS_CON | 0    |             |

| 8   | RS232_CTS_CON | I    |             |

| 9   | RS232_RI_CON  | I    |             |

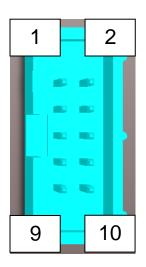

## J31 – COM 2 Header

**Description:** J31 is connected to the UART2 serial port (CMOS levels).

Connector: 3M D2510-6002-AR

#### Mating housing: TE 1658622-1 or equivalent

| Description | Туре | Signal Name | Pin | Pin | Signal Name | Туре | Description |

|-------------|------|-------------|-----|-----|-------------|------|-------------|

|             |      | N.C.        | 1   | 2   | N.C.        |      |             |

|             | I    | UART2_RXD   | 3   | 4   | UART2_RTS   | 0    |             |

|             | 0    | UART2_TXD   | 5   | 6   | UART2_CTS   | I    |             |

|             |      | N.C.        | 7   | 8   | N.C.        |      |             |

|             | G    | GND         | 9   | 10  | +3\/3       | PO   |             |

## J32 – Battery Holder

**Description:** J32 is used as a holder for a battery. If the board is powered off, the battery supplies an RTC clock chip and a touchscreen controller (optional).

Connector: MPD BA2032

Battery: GP CR2025 or equivalent

## J33 – System Header

**Description:** J33 connector brings out CPU-SPI2 interface and other various system signals.

Connector: 3M D2514-6002-AR

Mating housing: TE 1658622-2 or equivalent

www.iMX6Rex.com

| Description                                                         | Туре | Signal Name | Pin | Pin | Signal Name  | Туре | Description                                                      |

|---------------------------------------------------------------------|------|-------------|-----|-----|--------------|------|------------------------------------------------------------------|

|                                                                     | PO   | +3\/3       | 1   | 2   | PWR_LED_HDR  | 0    | Power good LED<br>output .<br>No series resistor is<br>required. |

| ON/OFF button                                                       | I    | PWR_BTN_HDR | 3   | 4   | USER_LED_HDR | 0    | User LED output. No series resistor is required.                 |

| Reset button                                                        | I    | RST_BTN_HDR | 5   | 6   | BUF_SYS_RSTn | 0    | Reset OUT for<br>external peripherals                            |

| I2C Expander GPIO<br>pin. This pin has<br>200kΩ pull up to<br>+3V3. | I/O  | GPIO6       | 7   | 8   | CPU_INT      | I    | General purpose<br>CPU interrupt                                 |

| I2C Expander GPIO<br>pin. This pin has<br>200kΩ pull down.          | I/O  | GPIO7       | 9   | 10  | + CSPI2_CS0  | 0    |                                                                  |

|                                                                     | I    | CSPI2_MISO  | 11  | 12  | CSPI2_MOSI   | 0    |                                                                  |

|                                                                     | G    | GND         | 13  | 14  | CSPI2_CLK    | 0    |                                                                  |

#### J34 – GPIO Header

**Description:** J34 is connected to six signals of the I2C GPIO Expander. Each GPIO signal has  $200k\Omega$  pull up / down resistor. Connector also brings out the I2C3 bus for a general purpose use.

Connector: 3M D2510-6002-AR

Mating housing: TE 1658622-1 or equivalent

| Description     | Туре | Signal Name | Pin | Pin | Signal Name | Туре | Description     |

|-----------------|------|-------------|-----|-----|-------------|------|-----------------|

|                 | PO   | +3V3        | 1   | 2   | GPIO0       | I/O  | pull up to +3V3 |

| pull up to +3V3 | I/O  | GPIO1       | 3   | 4   | GPIO2       | I/O  | pull up to +3V3 |

| pull down       | I/O  | GPIO3       | 5   | 6   | GPIO4       | I/O  | pull down       |

| pull down       | I/O  | GPIO5       | 7   | 8   | I2C3_SDA    | I/O  |                 |

|                 | G    | GND         | 9   | 10  | I2C3_SCL    | 0    |                 |

#### J35 – Power +5V Out Connector

**Description:** J35 is a +5V power output for a general use (e.g. as a 2.5" HDD power supply).

Connector: Molex 0532530470

Mating housing: Molex 0510650400 or equivalent

Mating crimps: Molex 0502128000 or equivalent

| Pin | Signal Name | Туре | Description             |

|-----|-------------|------|-------------------------|

| 1   | +5V         | PO   | +5V supply for a device |

| 2   | GND         | G    | Power ground            |

| 3   | GND         | G    | Power ground            |

| 4   | +5V         | PO   | +5V supply for a device |

## J36 – JTAG Header

**Description:** J36 is a JTAG header to debug the CPU.

Connector: TE 5103308-5

| Description | Туре | Signal Name | Pin | Pin | Signal Name | Туре | Description |

|-------------|------|-------------|-----|-----|-------------|------|-------------|

|             | 0    | JTAG_VREF   | 1   | 2   | +3V3        | PO   |             |

|             | I    | JTAG_nTRST  | 3   | 4   | GND         | G    |             |

|             | I    | JTAG_TDI    | 5   | 6   | GND         | G    |             |

|             | I    | JTAG_TMS    | 7   | 8   | GND         | G    |             |

|             | I    | JTAG_TCK    | 9   | 10  | GND         | G    |             |

|             | 0    | JTAG_RTCK   | 11  | 12  | GND         | G    |             |

|             | 0    | JTAG_TDO    | 13  | 14  | GND         | G    |             |

|             | I/O  | JTAG_nSRST  | 15  | 16  | GND         | G    |             |

|             | 0    | JTAG_DACK   | 17  | 18  | GND         | G    |             |

|             | G    | GND         | 19  | 20  | GND         | G    |             |

## J37 – Power Input Connector

**Description:** J37 is a main input power jack (input voltage range: +7V to +24V DC).

Connector: CUI PJ-002AH

Mating plug: Switchcraft S-760 or eqiuvalent

| Pin          | Signal Name | Туре | Description               |

|--------------|-------------|------|---------------------------|

| Center       | +V_INPUT    | ΡI   | Input power for the board |

| Outer barrel | GND         | G    | Power ground              |

#### J38 – ATX Power Connector

**Description:** J38 is an optional power connector. It can be used as a main power input for the board (+12V) or as an output connector (+5V) (e.g. for HDD supply). If +12V is required for the PCI Express Card (J3) or for the LVDS Backlight inverter (J19), this connector should be powered from an external source.

#### Connector: Molex 0015244449

| Pin | Signal Name | Туре | Description                                         |

|-----|-------------|------|-----------------------------------------------------|

| 1   | +12V_ATX    | PI   | +12V supply for the board                           |

| 2   | GND         | G    | Power ground                                        |

| 3   | GND         | G    | Power ground                                        |

| 4   | +5V_ATX     | PO   | +5V supply for the device (optional, see schematic) |

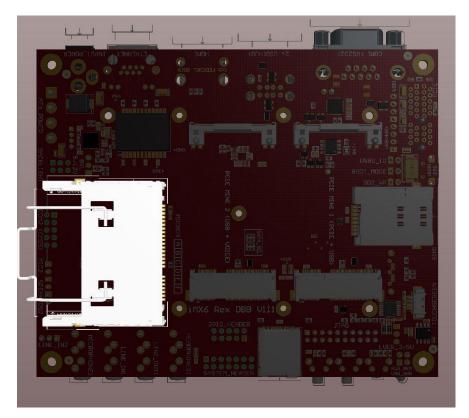

### J39 – Micro SD Slot 2

**Description:** J39 is connected to the CPU-SD2 interface. This slot is intended to be used as the main storage for the operating system. The card detection is supported. Write protection is controlled by JP3 jumper.

Connector: Hirose DM3C-SF

| Pin | Pin Name | Туре | Description        |

|-----|----------|------|--------------------|

| 1   | DAT2     | I/O  |                    |

| 2   | CD/DAT3  | I/O  |                    |

| 3   | CMD      | I/O  |                    |

| 4   | VDD      | PO   |                    |

| 5   | CLK      | 0    |                    |

| 6   | VSS      | G    |                    |

| 7   | DAT0     | I/O  |                    |

| 8   | DAT1     | I/O  |                    |

| 9   | SW       | I    | Card detection pin |

|     |          |      |                    |

## J40 – Touchscreen input header

**Description:** J40 is connected to the on board analog resistive touchscreen controller.

Connector: Molex 0532610471

Mating housing: Molex 0510210400 or equivalent

Mating crimps: Molex 0500588000 or equivalent

| Pin | Signal Name | Туре | Description      |

|-----|-------------|------|------------------|

| 1   | TS_Y+       | Ι    | Y+ channel input |

| 2   | TS_X+       | Ι    | X+ channel input |

| 3   | TS_Y-       | I    | Y- channel input |

| 4   | TS_X-       | I    | X- channel input |

#### J41 – LVDS Connector

**Description:** J41 is connected to the LVDS interface. Connector <u>J19</u> provides a backlight support for this interface. The display power can be selected between +5V and +3V3 by jumper J17.

Connector: JAE FI-SE20P-HFE

Mating housing: JAE FI-S20S or equivalent

Mating crimps: JAE FI-C3-A1-15000 or equivalent

| Pin | Signal Name | Туре | Description                              |

|-----|-------------|------|------------------------------------------|

| 1   | VCC_1       | PO   | +3V3 / +5V Supply for the display        |

| 2   | VCC_2       | PO   | +3V3 / +5V Supply for the display        |

| 3   | GND_1       | G    |                                          |

| 4   | GND_2       | G    |                                          |

| 5   | D0-         | 0    | LVDS D0 Negative signal                  |

| 6   | D0+         | 0    | LVDS D0 Positive signal                  |

| 7   | GND_3       | G    |                                          |

| 8   | D1-         | 0    | LVDS D1 Negative signal                  |

| 9   | D1+         | 0    | LVDS D1 Positive signal                  |

| 10  | GND_4       | G    |                                          |

| 11  | D2-         | 0    | LVDS D2 Negative signal                  |

| 12  | D2+         | 0    | LVDS D2 Positive signal                  |

| 13  | GND_5       | G    |                                          |

| 14  | CK-         | 0    | LVDS Clock Negative signal               |

| 15  | CK+         | 0    | LVDS Clock Positive signal               |

| 16  | GND_6       | G    |                                          |

| 17  | FRC         | 0    | Pulled up (10k $\Omega$ ) to LVDS supply |

| 18  | DPS         | 0    | Pulled down (10kΩ)                       |

| 19  | D3-/GND_7   | 0    | LVDS D3 Negative signal                  |

| 20  | D3+/GND_8   | 0    | LVDS D3 Positive signal                  |

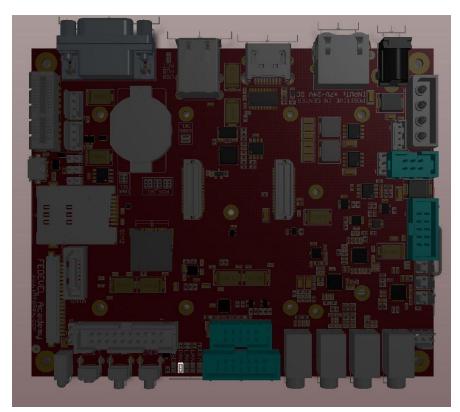

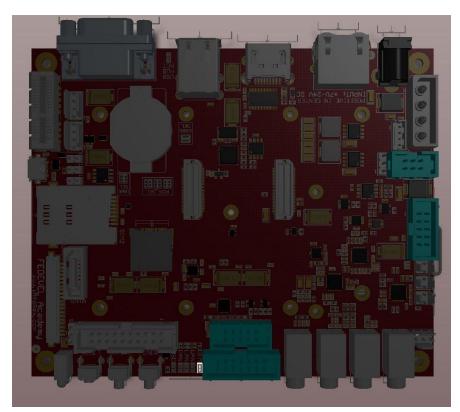

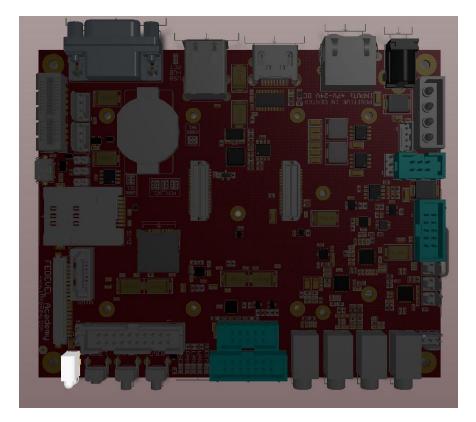

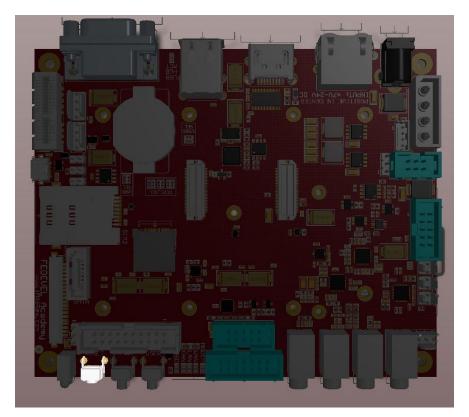

# Jumpers - Top

| Ref. Number | Function                              | Default position | Page |

|-------------|---------------------------------------|------------------|------|

| JP1         | USB0 ID selection                     | Pins closed      | 62   |

| JP2         | Boot mode selection                   | Pins left open   | 63   |

| JP3         | SD2 write protection                  | Pins closed      | 64   |

| <u>J17</u>  | LVDS Display supply voltage selection | Pin 2-3 closed   | 65   |

| <u>J18</u>  | Backlight voltage selection           | Pin 2-3 closed   | 66   |

#### JP1 – USB0 ID selection

**Description:** The JP1 header selects the level of the USB0\_ID signal. This signal controls the operation of the USB0 interface as a host or as a device.

| Pins   | Level of<br>USB0_ID | Description                       |

|--------|---------------------|-----------------------------------|

| Closed | GND                 | iMX6 REX acts as a host (default) |

| Open   | High                | iMX6 REX acts as a device         |

**Usage:** The main purpose of this pin is capability of USB0 to act as a device (e.g. in the case when you would like to connect iMX6 Rex to your PC and see it as a disk storage). A proper driver may be required.

#### JP2 – Boot mode selection

**Description:** The JP2 header controls the level of the Boot mode signal. This signal selects between booting from the on module SPI memory chip (default) or running in USB bootloader mode (used by MFGTools during manufacturing or debugging).

| Pins   | Level of<br>BOOT_MODE | Description                                 |

|--------|-----------------------|---------------------------------------------|

| Closed | GND                   | iMX6 Rex running in USB bootloader mode     |

| Open   | +3V0_ALWAYS           | Boots from the on module SPI chip (default) |

**Usage:** As a default the board boots up from the e-fuses. For special purpose the link on JP2 can be fitted. The board then boots from the serial downloader located in the USB0 host device.

Note: When running an iMX6 Rex module for the very first time (before eFUSES are programmed), this pin has to be left open to run the module in USB bootloader mode.

# JP3 – SD2 write protection

**Description:** JP3 header controls the write protection of the SD card inserted into SD2 card holder  $(\underline{J39})$ .

| Pins   | Level of<br>SD2_WP | Description                     |

|--------|--------------------|---------------------------------|

| Closed | GND                | SD card write enabled (default) |

| Open   | +3V3               | The SD card is write protected  |

#### J17 – LVDS Power Supply selection

**Description:** The header J17 selects display supply voltage on the  $\underline{J41}$  connector.

| Pins       | Level of<br>+VDD_LVDS | Description                        |

|------------|-----------------------|------------------------------------|

| Closed 1-2 | +5V                   | <u>J41</u> delivers +5V            |

| Closed 2-3 | +3V3                  | <u>J41</u> delivers +3V3 (default) |

| Open       | float                 | Not connected                      |

**Usage:** According to your display supply requirements connect the link. Many of the LVDS displays are supplied with +3V3 voltage. The +5V voltage is intended to be used in cases when an adapter is connected (e.g. LVDS to HDMI adapter, LVDS to DVI adapter, ....).

Warning: Before you connect your display, be sure you had selected the right voltage level, otherwise your display may be damaged!

### J18 – Backlight voltage selection

**Description:** The header J18 selects the voltage which will be present on the backlight connector  $\underline{J19}$  and will supply the backlight of the LVDS display ( $\underline{J41}$ ).

| Pins       | Level of<br>+BKLT_VCC | Description                  |

|------------|-----------------------|------------------------------|

| Closed 1-2 | +12_ATX               | For +12V backlights          |

| Closed 2-3 | +5V                   | For +5V backlights (default) |

| Open       | float                 | Not connected                |

Usage: Select the proper backlight voltage based on your backlight inverter requirements.

Warning: If you connect the wrong voltage to the backlight, the backlight inverter may be damaged!

Important: If you decide to supply the backlight with +12V, the board must be powered from an ATX Power Connector ( $\underline{J38}$ ).

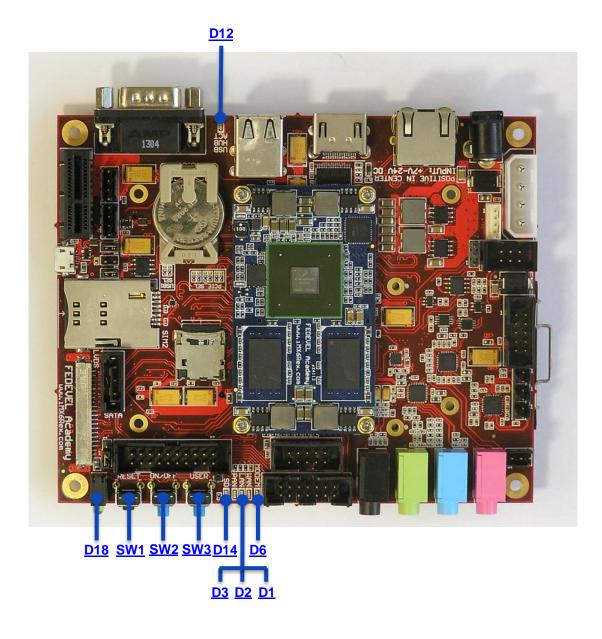

# LEDs & Buttons - Top

| Ref. Number | Function                    | Page |

|-------------|-----------------------------|------|

| <u>D1</u>   | PCIe Mini Card 1 WWAN       | 69   |

| <u>D2</u>   | PCIe Mini Card 1 WLAN       | 70   |

| <u>D3</u>   | PCIe Mini Card 1 WPAN       | 71   |

| <u>D6</u>   | PCIe Mini Card 2 WWAN       | 72   |

| <u>D12</u>  | USB0 Hub State indicator    | 73   |

| <u>D14</u>  | SD2 Activity indicator      | 74   |

| <u>D18</u>  | Power / User LED indicators | 75   |

|             |                             |      |

| <u>SW1</u>  | Reset button                | 76   |

| SW2         | Power button                | 77   |

| <u>SW3</u>  | User button                 | 78   |

## D1 – PCIe Mini Card 1 WWAN

**Description:** D1 indicates the PCIe Mini Card 1 WWAN activity. This signal depends on the card settings.

## D2 – PCIe Mini Card 1 WLAN

**Description:** D2 indicates the PCIe Mini Card 1 WLAN activity. This signal depends on the card settings.

## D3 – PCIe Mini Card 1 WPAN

**Description:** D3 indicates the PCIe Mini Card 1 WPAN activity. This signal depends on the card settings.

## D6 – PCIe Mini Card 2 WWAN

**Description:** D6 indicates the PCIe Mini Card 2 WWAN activity. This signal depends on the card settings.

#### D12 – USB0 Hub State indicator

Description: D12 indicates the state of the USB0 Hub.

| LED state | Description                 |

|-----------|-----------------------------|

| Off       | No USB device plugged in    |

| On        | An USB device is plugged in |

## D14 – SD2 Activity indicator

**Description:** D14 indicates that the SD2 interface is in the busy state (the card inserted into the <u>J39</u> holder). \**Note: This feature has to be supported in software.*

#### D18 – Power / User LED indicators

**Description:** D18 is a stacked LED indicator. The upper green diode is used for power good indication – the green diode is ON if all the powers are working correctly. The bottom red diode is a general purpose indicator and can be used by your application.

These two signals are also connected to the System header  $(\underline{J33})$  and can be take out from the board.

## SW1 – Reset button

**Description:** The SW1 button is used to reset the board. It is a hardware reset.

#### SW2 – Power button

**Description:** The SW2 button is used to power on and off the board. This signal is also available through the System header ( $\underline{J33}$ ). \**Note: This feature needs to be supported by software.*

#### SW3 – User button

**Description:** The SW3 button is a general purpose button and can be used by your application. This signal is also available on the System header ( $\underline{J33}$ ).

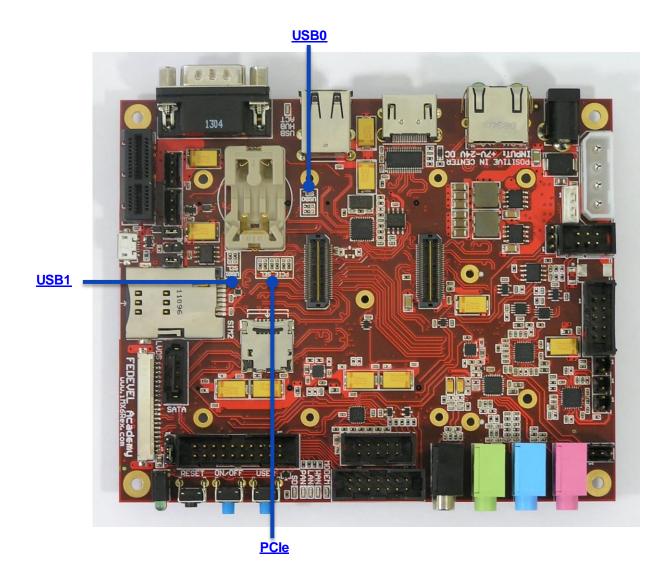

### **Peripheral selection resistors - Top**

The iMX6 Rex board includes several optional resistors, which can route selected peripherals to different type of connector (e.g. SATA can be routed to a standard SATA connector or CFAST slot)

# Peripheral selection resistors - Bottom

| Ref. Number | Function                 | Page |

|-------------|--------------------------|------|

| USB0        | USB0 Resistors Selection | 82   |

| USB1        | USB1 Resistors Selection | 83   |

| <u>PCle</u> | PCIe Resistors Selection | 84   |

| SATA        | SATA Resistors Selection | 85   |

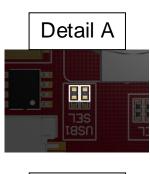

#### **USB0** Resistors Selection

**Description:** The USB0 interface can be routed either to the USB Hub or to the USB AB Micro connector (J21). When the USB Hub is selected, the USB stacked connector (J22), the USB Header (J23) and the PCIe Mini Card 2 (J9) can be used.

| Detail | <b>Resistors fitted</b> | USB0 connected to                     |

|--------|-------------------------|---------------------------------------|

| А      | R62, R65                | USB AB Micro connector ( <u>J21</u> ) |

| В      | R63, R67                | USB Hub (default)                     |

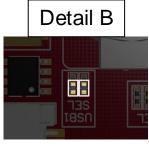

## **USB1** Resistors Selection

**Description:** The USB1 interface can be routed either to the PCIe Mini Card 1 ( $\underline{J4}$ ) or to the USB Header ( $\underline{J20}$ ).

| Detail | <b>Resistors fitted</b> | USB1 connected to                        |

|--------|-------------------------|------------------------------------------|

| А      | R64, R68                | USB Header ( <u>J20</u> )                |

| В      | R66, R69                | PCIe Mini Card 1 ( <u>J4</u> ) (default) |

### **PCIe Resistors Selection**

**Description:** The PCIe interface can be routed either to the PCIe x1 Slot ( $\underline{J3}$ ) or to the PCIe Mini Card 1 ( $\underline{J4}$ ).

| Detail | <b>Resistors fitted</b>      | PCIe connected to                        |

|--------|------------------------------|------------------------------------------|

| A      | R1, R3<br>R5, R8<br>R10, R14 | PCIe x1 Slot ( <u>J3</u> )               |

| В      | R2, R4<br>R7, R9<br>R12, R16 | PCIe Mini Card 1 ( <u>J4</u> ) (default) |

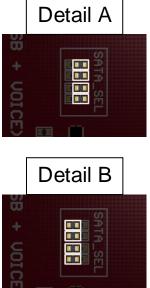

## **SATA Resistors Selection**

**Description:** The SATA interface can be routed either to the SATA Connector ( $\underline{J14}$ ) or to the CFAST Socket ( $\underline{J15}$ ).

| Detail | Resistors fitted     | SATA connected to                     |

|--------|----------------------|---------------------------------------|

| А      | R36, R38<br>R40, R42 | SATA Connector ( <u>J14</u> )         |

| В      | R37, R39<br>R41, R43 | CFAST Socket ( <u>J15</u> ) (default) |